TMS<?xml:namespace prefix = st1 ns = "urn:schemas-microsoft-com:office:smarttags" />320C31 基于 IMP16C554 的多串口通信设计<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

佘霁频

(南京航空航天大学信息科学与技术学院,江苏省南京市210016)

【摘 要】 围绕通用异步发送和接收(UART)芯片IMP16C554,对TMS320C31 芯片如何与外界进行多串口的异步通信给出了一种较为可行的电路设计,重点阐述了对芯片IMP16C554 的初始化编程设置及其基于先进先出(FIFO)查询工作模式的接口编程设计。

关键词:数字信号处理,UART 芯片,FIFO

中图分类号:TP334.7

0 引 言

随着信息技术和计算机技术的飞速发展,数字信号处理器(DSP)芯片的发展日新月异,其功能日益强大,已被广泛应用于当今科技和国民经济的各个领域。串口异步通信在数据通信方式中占据主导地位,因此,它与DSP在通信领域设计过程中的结合,特别是利用DSP的特点与外界进行多串口异步通信的设计显得尤

为重要。

1 TMS320C31 串口扩展电路的设计

TMS320C31 是TI公司的第3代浮点运算DSP芯片,它将浮点运算与定点运算结合,具有更高的精度,并且不必考虑运算的溢出问题,因此,该芯片具有更好的性能,更容易在系统的处理器上实现高级语言。由于TMS320C31 本身仅具有一个串口,因此要与其进行多串口的通信就必须配以某种专用的多串口通信接口芯片来进行外围电路的扩展。

1.1 UART 接口芯片

本设计采用的 IMP16C554 是一款带16字节收发先进先出(FIFO)的串行接口芯片,它共具有4个通用异步发送和接收(UART)接口。IMP16C554自身包含一个可编程波特率发生器,可产生50Hz~1.5 MHz 的任一收发频率,还具备标准的Modem 接口和自测功能。

此外,IMP16C554 还具有如下主要特性:16字节带错误标志的接收FIFO;Modem 控制信号( CTS*,RTS*,DSR*,DTR*,RI*,CD*);可编程字符长度(5,6,7,8);奇、偶或无奇偶位的产生和校验;状态报告寄存器;独立的收发控制;TTL 兼容的输入输出;软件与Ei8250 和Ei16C550 兼容;7.372 MHz 晶振或外部时钟源下460.8 kHz 的收发操作。

1. 2 串口扩展电路

用IMP16C554 实现对TMS320C31 多串口异步通信的扩展,主要应处理好两者之间的通信接口问题,其中应包括接口芯片与DSP 总线直接相连的一组数据线、两者之间进行联络的应答信号以及产生片选信号和内部寄存器地址选择的一个地址译码电路。

此外,本设计中采用美国EIA 制定的RS-232C作为串行通信的接口标准,由于该标准用正负电压表示逻辑状态,而与TTL 器件以高低电平表示逻辑状态的规定不同,因此,在串行口与接口芯片这一TTL 器件连接之前必须进行电平和逻辑关系的变换。为此,本设计中选用MAX232 芯片来完成TTL↔EIA 的双向电平转换。

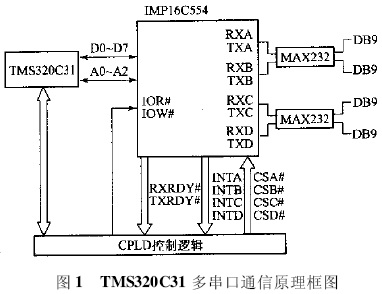

综上所述,设计的电路原理框图如图1 所示。

复杂可编程逻辑器件(CPLD)控制逻辑模块接收分别来自4 个UART 的中断请求(INTA ~ INTD)及收发FIFO 的就绪信号(RXRDY#、TXRDY#),以此联络DSP 芯片并根据相应的读写时序产生对IMP16C554的片选(CSA# ~ CSD#)、读写(IOR#、IOW#)信号以及反馈给TMS320C31 的等待信号。

2 通信编程设计

在与TMS320C31 进行多串口异步通信的设计中,串口芯片如何有序地进行数据的收发操作是编程设计的重点。IMP16C554 的收发操作均有“0”和“1”两种

模式。在“0”模式下,收发操作仅根据它们的保持寄存器或FIFO 缓冲器中有无字符而确定就绪信号RXRDY#或TXRDY#的走高或走低。而“1”模式下,则只是根据FIFO 缓冲器中的字符是否已满而发出相应的收发就绪信号。为了提高收发数据的工作效率,不至于每收到或发送1个字符就产生一次就绪中断,本文的串口设计选择采用"1"模式下的16字节FIFO缓冲器的收发操作。

2.1 UART 的初始化编程设置

UART 的初始化工作即是对其内部各寄存器初始值的设置。IMP16C554 共有12 个可用的寄存器,分别为RHR、THR、IER、FCR、ISR、LCR、MCR、LSR、MSR、

SPR、DLL、DLM。对这些寄存器的访问分别是在读和写操作的两种模式下由地址线A2 ~ A0 进行译码选择。在接口编程的初始化设置中主要有两方面工作: 一是设置在“1”模式收发操作下FIFO 的具体工作模式;二是设置异步数据通信的格式。

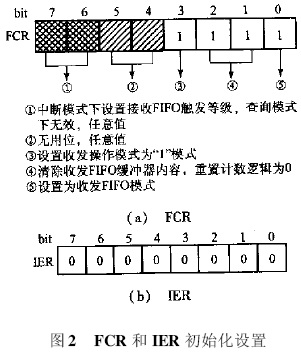

IMP16C554 的FIFO 具有两种工作模式:中断模式和查询模式。由于FIFO 缓冲器使数据丢失的可能性极小,而在许多应用中使用中断也并不那么重要,因此

本例编程设计选择FIFO 的查询工作模式。在查询应用中,IMP16C554 减少过速或欠载运行的性能也将得到很好的发挥。对FIFO 查询操作的设置主要涉及2个寄存器:FIFO 控制寄存器(FCR)和中断允许寄存器(IER)。对其初始化的写入字如图2 所示。

IER 中bit 3 ~ bit 0 的置零分别表示以下中断使能的关闭:bit 3 为Modem 状态寄存器中断;bit 2 为接收器线路状态中断;bit 1 为发送器空中断;bit 0 为接收器就绪中断。

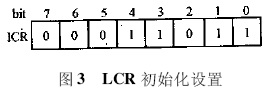

IMP16C554 的线路控制寄存器(LCR)用来定义异步数据通信格式,它包括字符长度、停止位位数和奇偶校验的设定。bit 1 和bit 0 决定字符长度(见表1);bit2 决定对应于字符长度的停止位位数(见表2);bit 3决定是否存在奇偶校验(0 表示无奇偶校验,1 表示在传输过程中会产生1 位奇偶校验);bit 4 是在存在检验的情况下决定奇偶校验的格式(0 表示奇校验,1 表示偶校验);bit 5 是结合bit 4 强制决定奇偶比特位的格式(见表3);bit 6 是突发控制位(0 表示一般操作条件,1 表示迫使发送引脚TX 变低);bit 7 表示关闭内部波特率计数器使能(0 表示一般操作,1 表示选择除数关闭寄存器)。

表1 LCR 的bit 0 和bit 1

bit 1 | bit 0 | 字符长度 |

0 | 0 | 5 |

0 | 1 | 6 |

1 | 0 | 7 |

1 | 1 | 8 |

表2 LCR 的bit 2

bit 1 | 字符长度 | 停止位/s |

0 | 5,6,7 | 1 |

1 | 5 | 1~1/2 |

1 | 6,7,8 | 2 |

表3 LCR 的bit 4 和bit 5

bit 5 | bit 4 | 奇偶校验位 |

1 | 0 | 1 |

1 | 1 | 0 |

结合上述分析,将本例中通信格式设置为字符长度为8、带1个停止位、对数据进行偶校验(不强制设校验位)的LCR 初始化写入字如图3 所示。

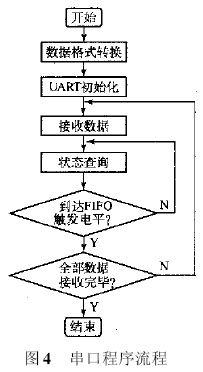

2.2 基于FIFO 查询工作模式的接口编程

在与TMS320C31 多串口通信的设计中,IMP16C554 是以并行接口方式与DSP 通信的,它参与TMS320C31 对存储器及外设I/O 的统一编址,因此,它的初始化工作实际上是通过对DSP 的编程来实现的。在软件编程设计中,虽然接收和发送FIFO 是两个独立工作的缓冲器,但它们的工作原理相同,即对于不同的数据来源和目的地都是相应的接收及发送数据的过程。具体说来,IMP16C554 的接收缓冲器实际上是接收来自串行口( 本设计中的DB9)的外部数据而将其发往DSP 进行数据处理,而发送缓冲器则是接收来自DSP 的数据,然后将其发送至串行口。因此,其软件设计的机理相同。图4 给出基于FIFO 查询工作模式的串口程序流程。

程序中,对UART 进行初始化设置后,DSP 分别对两个FIFO 缓冲器发出接收或发送数据的命令,无论对哪一个,都将首先开始接收来自DSP 或通信线路的异步通信数据,而程序也会不断检查相对应的缓冲器是否已满。在接收命令下,若缓冲器未满,RXRRDY#会一直处于低电平状态,直到缓冲器已接收满16 字节的数据,则RXRDY#才会突变为一个FIFO 的触发高电平以表示此一轮数据接收已完毕;而后若还有其他数据需要接收,则再进行下一轮工作。同样,在发送命令下,直到缓冲器接收满16个字节的数据前,TXRDY#都会一直保持高电平状态,而一旦它突变为一个FIFO的触发低电平,则表示该缓冲器内的数据此时可以向外发送。而当它再次变高时则表示又可以开始进行新一轮待发数据的接收了,直到全部数据都发送完毕。

3 结束语

本文主要围绕通用串口芯片IMP16C554,对与DSP 芯片TMS320C31 的多串口通信给出了一种可行的电路原理设计,并就UART 的初始化编程设置进行了分析,最后给出了基于UART 的FIFO 查询模式的接口编程设计。本设计中TMS320C31 是TI 公司浮点DSP 芯片的典型代表,因此对与其进行多串口通信的研究具有一定的应用价值。

参 考 文 献

[1]王念旭,等。 DSP 基础与应用系统设计。 北京:北京航空航天大学出版社,2001

[2]李现勇。 Visual C++ 串口通信技术与工程实践。 北京:人民邮电出版社,2002

[3]张雄伟,曹铁勇。 DSP 芯片的原理与开发应用( 第2 版)。电子工业出版社,2000

Design of TMS320C31 Multi-uart Communication Based on IMP16C554

She Jipin

(Nanjing University of Aeronautics and Astronautics,Nanjing 210016,China)

【Abstract】 TMS320C31 is a floating point DSP chip from Texas Instruments and it's widely used to design the circuit for multi-ports UART(universal asynchronous receiver and transmitter )communication with the chip。 Employing the UART chip IMP16C554,this paper provides such a design。 It also analyzes the initialization programming for UART in detail and puts forward an interface program design based on a FIFO inquiring operation mode for IMP16C554。

Keywords:DSP,UART Chip,FIFO

/3

/3

文章评论(0条评论)

登录后参与讨论