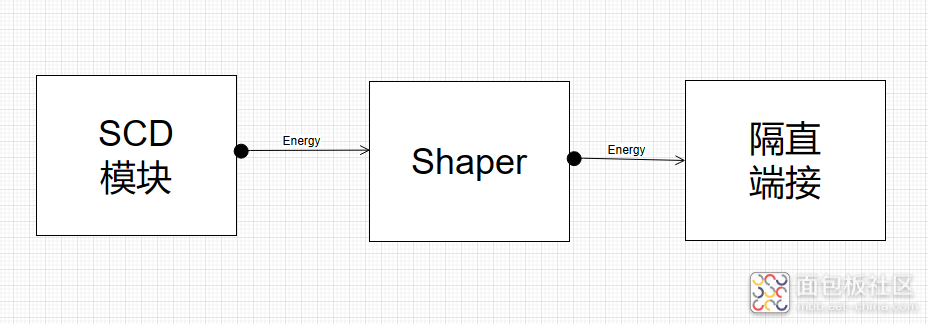

概述 SiPM三代电路的电源供电独立之后,确实发现效果要比2代好。本文主要讨论三代的2Dmap测试,通过与二代的比较找到电路改版带来的改进效果。除了供电改动,能量分支还有一处最大改动是预留了图1所示的输出端接及直流处理部件。 图1:整形输出保留端接与直流处理部件 三代SiPM读出测试系统2Dmap测试记录 板子完成制作后,完成硬件检测后,首先开展了2Dmap测试。 测试1 :如果图1最 右侧的部件未使用,即均直接焊接0欧姆电阻,或者直接短接。此时在使用Na22源的情况下,测试结果不理想,全局平均能谱分辨率大概在12%左右,2Dmap结果与二代差不多,即依然存在拖影。 测试2 :使用另一块板子,焊接上隔直端接部件,得到的测试结果如图2,结果中右下角有3个点缺失,这是硬件物理上原因造成。更换部件参数后,得到类似结果,故添加该部件可以解决拖影问题。 图2:添加隔直端接部件后解决了2Dmap中的拖影问题 测试3 :上述2dmap点缺失问题,有几个可能原因,一个是焊接厂在焊接SiPM的时候为了标识起始引脚位置,在SiPM树脂表面用记号笔添加了标识,如图3。该记号无法清除,所以影响了记号对应SiPM通道对信号的探测。此外还有一个可能,是对应通道的能量信号或者时间信号缺失造成,比如比较器工作异常导致时间脉冲无法正常产生,这样是会应该能量计算的。 图3:SiPM表面错误添加的记号标识 测试4 :在检查硬件电路未发现其它异常的情况下,最终归结为上述记号导致该问题。为了验证,又进行下述测试,如图4所示,使用贴纸人为遮蔽SiPM的一角,然后完成数据采集,得到2dmap结果。 图4:表面遮蔽后重做2dmap测试 测试5 :保留串接电容,使用Cs-137测试2dmap,测试结果如图5所示,图左使用了100mV能量阈值,图右使用了50mV的能量阈值。可以看到高能量阈值设置时,7x7阵列中的中间点不是很清晰。还需要注意的是,阈值降低可以将能谱分辨率从10.5%提升到8.4%。 图5:使用Cs-137源在不同能量阈值下得到的2Dmap测试结果 测试6 :保留串接电容,使用Na22测试2dmap,测试结果如图6所示。和Cs137类似,中间点在高能量阈值时也是不太清晰。另外,Na22在两种能量阈值下,得到了大致相同的能谱分辨率,大概在9.2%左右。与测试1对比,可以发现能谱分辨率提升了不少。(注:在测试过程中还有特殊情况出现,即在保留串接电容的时候,上电后需要等待几分钟时间,否则测量得到的能谱分辨率也不理想。电容充放电的干扰?) 图6:使用Na22源在不同能量阈值下得到的2Dmap测试结果 对于上述能谱分辨率在上电后不同时刻采集数据差异,如表1所示: 表1:使用Cs137时不同上电后不同时刻采集数据得到的结果 Energy resolution = 14% Energy resolution = 8.4% Energy resolution = 14% Energy resolution = 8.4% Crystal ID No. Peak Position Crystal ID No. Peak Position Crystal ID No. Peak Position Crystal ID No. Peak Position 0 162 0 150 25 219 25 200 1 193 1 178 26 224 26 207 2 204 2 189 27 194 27 178 3 195 3 180 28 199 28 184 4 192 4 177 29 234 29 217 5 184 5 170 30 236 30 219 6 155 6 144 31 221 31 203 7 174 7 160 32 227 32 209 8 206 8 189 33 223 33 206 9 221 9 204 34 173 34 159 10 224 10 206 35 182 35 168 11 224 11 207 36 210 36 195 12 202 12 186 37 218 37 202 13 181 13 167 38 210 38 192 14 191 14 176 39 216 39 198 15 218 15 201 40 210 40 194 16 237 16 219 41 161 41 148 17 237 17 219 42 146 42 134 18 236 18 218 43 157 43 144 19 216 19 199 44 166 44 152 20 200 20 185 45 187 45 166 21 201 21 186 46 192 46 176 22 216 22 199 47 185 47 171 23 241 23 224 48 154 48 142 24 242 24 222 附:二代与三代SiPM读出测试系统2Dmap对比(主要是拖影的消失) 图7:二代与三代SiPM读出系统2Dmap测试结果对比

标签: 2d

标签: 2d