数字系统一般可分为控制单元和数据通道,数据通道通常由组合逻辑和逻辑电路构成,而控制单元通常由时序逻辑电路构成.控制单元的每一个控制态可以看作一种状态,而状态之间的转换条件指定了下一个状态和输出信号,因此采用有限状态机可以非常清楚地描述时序电路之间的状态转换模式和状态转换的条件.

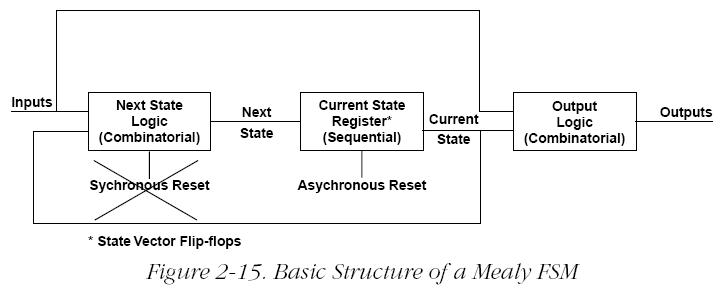

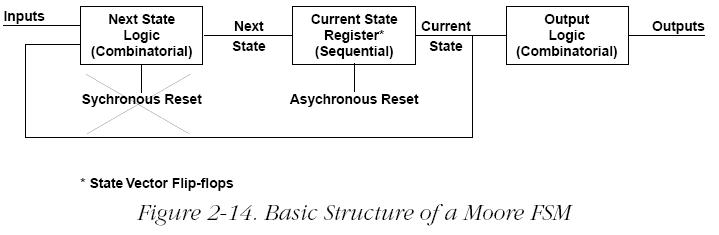

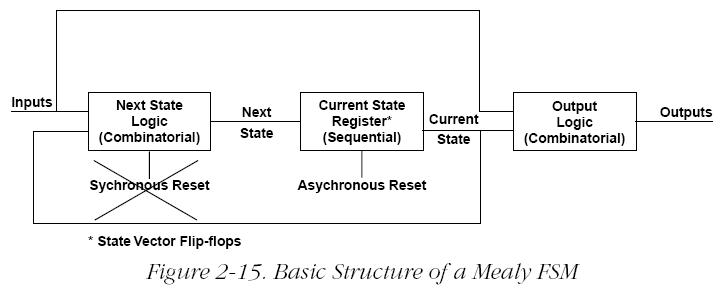

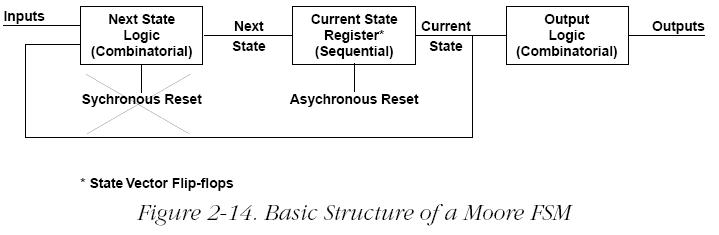

有限状态机根据输出信号与当前以及输入信号的关系来分,可以分为Moore型和Mealy型两种:输出信号只和当前状态有关的状态机称为Moore型状态机,如图2-14;输出信号不仅与当前与状态有关,而且也和输入信号有关的状态机称为Mealy型状态机,如图2-15.

以Mealy型FSM举例,状态图如下:

VHDL代码如下:

-- Example of a 5-state Mealy FSM

library ieee;

use ieee.std_logic_1164.all;

entity mealy is

port (clock, reset: in std_logic;

data_out: out std_logic;

data_in: in std_logic_vector (1 downto 0));

end mealy;

architecture behave of mealy is

type state_values is (st0, st1, st2, st3, st4);

signal pres_state, next_state: state_values;

begin

-- FSM register

statereg: process (clock, reset)

begin

if (reset = '0') then

pres_state <= st0;

elsif (clock'event and clock ='1') then

pres_state <= next_state;

end if;

end process statereg;

-- FSM combinational block

fsm: process (pres_state, data_in)

begin

case pres_state is

when st0 =>

case data_in is

when "00" => next_state <= st0;

when "01" => next_state <= st4;

when "10" => next_state <= st1;

when "11" => next_state <= st2;

when others => null;

end case;

when st1 =>

case data_in is

when "00" => next_state <= st0;

when "10" => next_state <= st2;

when others => next_state <= st1;

end case;

when st2 =>

case data_in is

when "00" => next_state <= st1;

when "01" => next_state <= st1;

when "10" => next_state <= st3;

when "11" => next_state <= st3;

when others => null;

end case;

when st3 =>

case data_in is

when "01" => next_state <= st4;

when "11" => next_state <= st4;

when others => next_state <= st3;

end case;

when st4 =>

case data_in is

when "11" => next_state <= st4;

when others => next_state <= st0;

end case;

when others => next_state <= st0;

end case;

end process fsm;

-- Mealy output definition using pres_state w/ data_in

outputs: process (pres_state, data_in)

begin

case pres_state is

when st0 =>

case data_in is

when "00" => data_out <= '0';

when others => data_out <= '1';

end case;

when st1 => data_out <= '0';

when st2 =>

case data_in is

when "00" => data_out <= '0';

when "01" => data_out <= '0';

when others => data_out <= '1';

end case;

when st3 => data_out <= '1';

when st4 =>

case data_in is

when "10" => data_out <= '1';

when "11" => data_out <= '1';

when others => data_out <= '0';

end case;

when others => data_out <= '0';

end case;

end process outputs;

end behave;

/1

/1

文章评论(0条评论)

登录后参与讨论