JTAG接口的出处就不多做介绍了,自己在网上可以找到不少的资料。

JTAG_TAP接口有4个主要的信号线,分别是TCK,TDI,TDO,TMS;还有一些可选的信号线,如RTCK,TRST。

TCK信号为TAP接口的同步时钟信号。

TDI和TDO分别为TAP接口的输入和输出信号。

TMS用于控制TAP的状态。

RTCK为TCK信号的返回信号,一般用于TCK速度的自动调整(LPCARM还使用这个信号来使能JTAG接口)。

TRST为TAP的复位信号,根据TAP状态转换图,可以使用5个'1'的TMS信号来替代。

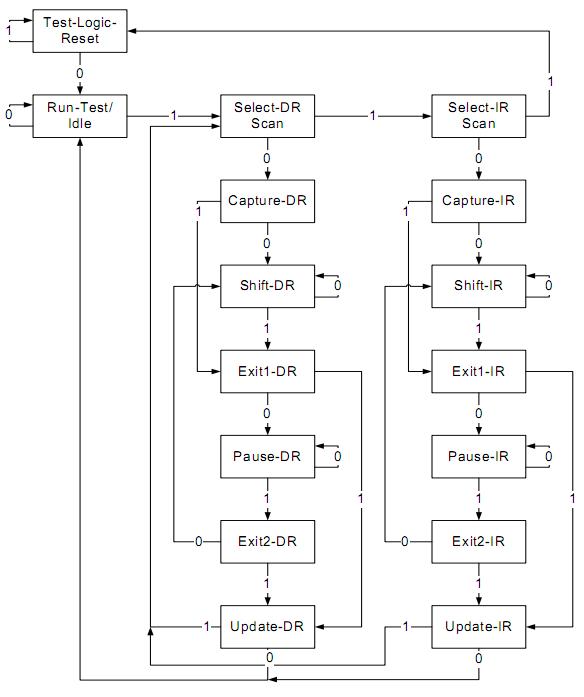

TAP状态转换图:

其中,各个状态的带箭头的连线上的数字为TMS信号,也就是说TMS信号控制着TAP接口的状态。

虽然状态看似比较多,但一般有意义的只有几个:TLR(Test-Logic-Reset)、RTI(Run-Test/Idle)、Capture-IR、Capture-DR、Shift-IR、Shift-DR、Update-IR、Update-DR这么一些,其他的状态都是浮云(或者说路过)。TAP接口主要控制着2个'寄存器':IR(命令寄存器)和DR(数据寄存器)。

TAP主要操作有3个:

1.TAP复位,可以通过TRST或者TMS上输出5个'1'(进入TLR状态)来实现

2.读写IR

3.读写DR

可能了解ARM调试接口的人会说,在通过JTAG接口给ARM核总线写入指令后,需要控制在RTI状态下的TCK周期。确实,不过我认为这个控制是读写IR或者DR的一个参数。如果这个参数是0,这TAP会停留在Update-IR或者Update-DR,如果>0,则会在RTI状态上停留n个周期。

如果归结到程序上,可以实现3个函数(除了延时函数外):

Access_IR,Access_DR,Write_TMS

接下来就是关键了,如果使用低成本的单片机来实现这个接口(不使用IO口来模拟)

当然,这个对单片机是有一定要求的,需要有2路硬件SPI兼容接口(有些单片机的USART可以工作在SPI模式下),一路为主SPI,一路为从SPI。

把这2路SPI接口的SCK接在一起,作为TCK信号;主SPI接口的MISO作为TDO,MOSI作为TDI;从SPI接口的MISO作为TMS。这样,通过这2路SPI接口,就可以实现一个硬件的JTAG接口。当然,还是有一些限制的,比如,所有的操作必须以字节为单位,2次SPI操作间,由于需要运行程序,所以也会有一些延时。

为了弥补操作必须以字节为单位这个缺陷,可以利用Pause-IR和Pause-DR状态下,无论输出多少个TMS'0',都不会影响结果的特性,来解决。也就是说,当需要执行的操作有小于8位的余量时,可以在Pause-XR状态下填补一些'0',这样就可以使每个操作都凑成字节操作。

代码:

可以参考Versaloon的实现代码中的JTAG.c文件,里面的代码还考虑到了实现JTAG菊花链时,需要的额外处理。

验证项目(计划中):

VJFlasher -- Versaloon Jtag Flasher,可以通过xml格式的配置文件简单的增加对各种芯片的支持(虽说简单是指不需要修改程序)

- 上一篇: Versaloon + XXXXXX

- 下一篇: VJFlasher的一些构思

用户131114 2009-7-27 18:43

用户146821 2009-7-27 14:04

用户131114 2008-12-1 11:35

用户472164 2008-11-30 15:58

用户472164 2008-11-30 15:58