使用了各种不同方式实现了JTAG接口,充分了解了性能瓶颈,和一些操作策略。当然,这里的所有优化都是在STM32版的Versaloon上进行的,针对低成本的JTAG方案。

第一个优化:让JTAG工作在DMA方式

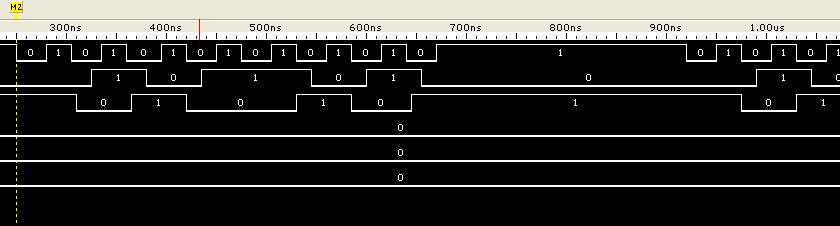

JTAG频率比较高的时候,如果使用低成本的MCU,通过2路SPI的方式来实现的话,在SPI每个数据间,会有一定的延时。见图:

这个是SPI在异步操作方式下的波形,可见,2个字节之间的延时是非常的明显的,这种情况下,虽然JTAG运行在18M,但平均速度只有8M。

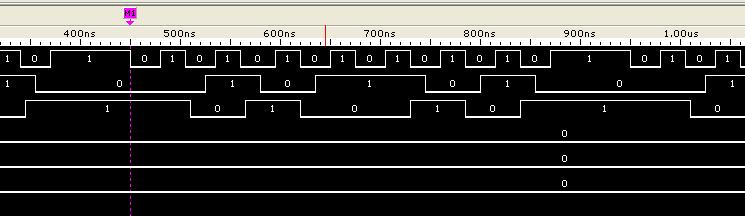

这样,可以使用DMA的方式来操作其中一路SPI接口,波形如下:

2个字节间的延时明显缩短,18MJTAG下平均速度为13M。如果要消除这个延时,可能要用到CPLD了。

2路SPI都使用DMA操作:

18M的JTAG频率下,平均速度为16M。

不过,这2种(ASYN和DMA)方式下,OpenOCD中的驱动代码不同,使用DMA方式的代码要简单很多。当使用4.5M的JTAG速度时,使用ASYN方式下,2个字节间也可以明显看到延时,但在DMA方式下,已经看不出来延时,波形是连续的。但对LPC2148的RAM下载速度确基本一样(使用fast_load命令测试,使能了DCC和fast_memory_access,关闭了IR读取校验)。可见,速度不高的时候,瓶颈并不在JTAG上。

第二个优化:USB接口优化,使用double buffer

同样在4.5M的JTAG下对LPC2148进行RAM下载,不使用双缓存时,速度为71KB/s左右;使用了双缓冲时,速度一下子飙到了95KB/s。可见,USB是非常关键的性能瓶颈。

其中,USB接收使用双缓存的效果比较明显,USB发送使用双缓存的效果就不太明显了。当然也有可能是USB发送双缓存操作代码的问题,因为ST没有提供示例代码,已经联系ST的ARM部门的技术支持,以确认submitted,等待回复结果。

由此,大概估算Versaloon在18M下的性能,相信应该可以超过200KB/s。如果以后为Versaloon做高端版本的话,现在也非常清楚性能的瓶颈(其实以前就很清楚了,现在有了定量的数据)。

/5

/5

文章评论(0条评论)

登录后参与讨论