FPGA的开发流程和关键步骤的含义<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

综合(Synthesize):就是将HDL语言、原理图等设计输入翻译成由与、或、非门和RAM、触发器等基本逻辑单元的逻辑连接(网表),并根据目标和要求(约束条件)优化所生成的逻辑连接,生成EDF文件。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

实现(Implement):是将综合输出的逻辑网表翻译成所选器件的底层模块与硬件原语,将设计映射到器件结构上,进行布局布线,达到在选定器件上实现设计的目的。实现主要分为3个步骤:翻译(Translate)逻辑网表,映射(Map)到器件单元与布局布线(Place & Route)。

翻译(Translate)的主要作用是将综合输出的逻辑网表翻译为Xilinx特定器件的底层结构和硬件原语(具体的源语详见ISE中language templates)。

映射(Map)的主要作用是将设计映射到具体型号的器件上(LUT、FF、Carry等)。

布局布线(Place & Route)步骤调用Xilinx布局布线器,根据用户约束和物理约束,对设计模块进行实际的布局,并根据设计连接,对布局后的模块进行布线,产生FPGA/CPLD配置文件。

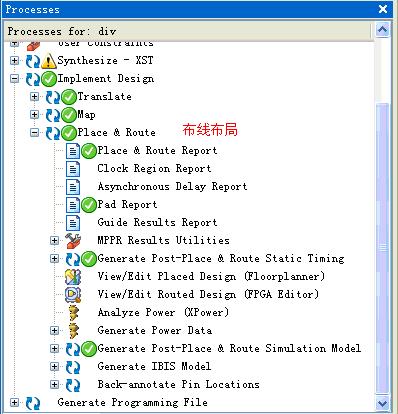

ISE中实现步骤的功能选项

翻译项目包括3个命令:

【Translation Report】用以显示翻译步骤的报告;

【Floorplan Design】用以启动Xilinx布局规划器(Floorplanner)进行手动布局,提高布局器效率;

【Generate Post-Translate Simulation Model】用以产生翻译步骤后仿真模型,由于该仿真模型不包含实际布线时延,所以有时省略此仿真步骤。

映射项目包括如下命令:

【Map Report】用以显示映射步骤的报告;

【Generate Post-Map Static Timing】产生映射静态时序分析报告,启动时序分析器(Timing Analyzer)分析映射后静态时序;

【Manually Place & Route (FPGA Editor)】用以启动FPGA底层编辑器进行手动布局布线,指导Xilinx自动布局布线器,解决布局布线异常,提高布局布线效率;

【Generate Post-Map Simulation Model】用以产生映射步骤后仿真模型,由于该仿真模型不包含实际布线时延,所以有时也省略此仿真步骤。

布局布线步骤的命令与工具非常多:

【Place & Route Report】用以显示布局布线报告;

【Asynchronous Delay Report】用以显示异步实现报告;

【Pad Report】用以显示管脚锁定报告;

【Guide Results Report】用以显示布局布线指导报告,该报告仅在使用布局布线指导文件NCD文件后才产生;

【Generate Post-Place & Route Static Timing】包含了进行布局布线后静态时序分析的一系列命令,可以启动Timing Analyzer分析布局布线后的静态时序;

【View/Edit Place Design(Floorplanner)】和【View/Edit Place Design(FPGA Editor)】用以启动Floorplanner和FPGA Editor完成FPGA布局布线的结果分析、编辑,手动更改布局布线结果,产生布局布线指导与约束文件,辅助Xilinx自动布局布线器,提高布局布线效率并解决布局布线中的问题;

【Analyze Power(XPower)】用以启动功耗仿真器分析设计功耗;

【Generate Post-Place & Route Simulation Model】用以产生布局布线后仿真模型,该仿真模型包含的时延信息最全,不仅包含门延时,还包含了实际布线延时。该仿真步骤必须进行,以确保设计功能与FPGA实际运行结果一致;

【Generate IBIS Model】用以产生IBIS仿真模型,辅助PCB布板的仿真与设计;

【Multi Pass Place & Route】用以进行多周期反复布线;

【Back-annotate Pin Locations】用以反标管脚锁定信息。

参考资料:

/5

/5

文章评论(0条评论)

登录后参与讨论