NAND与处理器的连接

选择内置NAND接口的处理器或控制器的好处很多。如果没有这个选择,有可能在NAND和几乎任何处理器之间设计一个“无粘接逻辑

(glueless)”接口。NAND和NOR闪存的主要区别是复用地址和数据总线。该总线被用于指定指令、地址或数据。CLE信号指定指令周期,而

ALE信号指定地址周期。利用这两个控制信号,有可能选择指令、地址或数据周期。把ALE连接到处理器的第五地址位,而把CLE连接到处理器的第四地址

位,就能简单地通过改变处理器输出的地址,任意选择指令、地址或数据。这容许CLE和ALE在合适的时间自动设置为低。

为了提供指令,处理器在数据总线上输出想要的指令,并输出地址0010h;为了输出任意数量的地址周期,处理器仅仅要依次在处理器地址

0020h之后输出想要的NAND地址。注意,许多处理器能在处理器的写信号周围指定若干时序参数,这对于建立合适的时序是至关重要的。利用该技术,你不

必采用任何粘接逻辑,就可以直接从处理器存取指令、地址和数据。

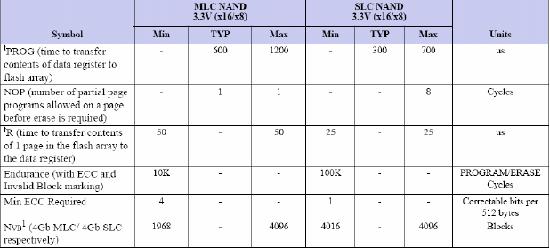

多层单元

多层单元(MLC)的每一个单元存储两位,而传统的SLC仅仅能存储一位。MLC技术有显著的密度优越性,然而,与SLC相比(表3),其速度或可靠性稍逊。因此,SLC被用于大多数媒体卡和无线应用,而MLC器件通常被用于消费电子和其它低成本产品。

如上所述,NAND需要ECC以确保数据完整性。NAND闪存的每一个页面上都包括额外的存储空间,它就是64个字节的空闲区(每512字节的扇区

有16字节)。该区能存储ECC代码及其它像磨损评级或逻辑到物理块映射之类的信息。ECC能在硬件或软件中执行,但是,硬件执行有明显的性能优势。在编

程操作期间,ECC单元根据扇区中存储的数据来计算误码校正代码。数据区的ECC代码然后被分别写入到各自的空闲区。当数据被读出时,ECC代码也被读

出;运用反操作可以核查读出的数据是否正确。

有可能采用ECC算法来校正数据错误。能校正的错误的数量取决于所用算法的校正强度。在硬件或软件中包含ECC,就提供了强大的系统级

解决方案。最简单的硬件实现方案是采用简单的汉明(Simple

Hamming)码,但是,只能校正单一位错误。瑞德索罗门(Reed-Solomon)码提供更为强大的纠错,并被目前的控制器广为采用。此外,BCH

码由于比瑞德索罗门方法的效率高,应用也日益普及。

要用软件执行NAND闪存的区块管理。该软件负责磨损评级或逻辑到物理映射。该软件还提供ECC码,如果处理器不包含ECC硬件的话。编程或擦除操作之后,重要的是读状态寄存器,因为它确认是否成功地完成了编程或擦除操作。如果操作失败,要把该区块标记为损坏且不能再使

用。以前已编写进去的数据要从损坏的区块中搬出,转移到新的(好的)存储块之中。2Gb

NAND的规范规定,它可以最多有40个坏的区块,这个数字在器件的生命周期(额定寿命为10万次编程/擦除周期)内都适用。一些有坏块的NAND器件能

够出厂,主要就归根于其裸片面积大。管理器件的软件负责映射坏块并由好的存储块取而代之。

利用工厂对这些区块的标记,软件通过扫描块可以确定区块的好坏。坏块标记被固定在空闲区的第一个位置(列地址2048)。如果在0或1

页的列地址2048上的数据是“non-FF”,那么,该块要标记为坏,并映射出系统。初始化软件仅仅需要扫描所有区块确定以确定哪个为坏,然后建一个坏

块表供将来参考。小心不要擦除坏块标记,这一点很重要。工厂在宽温和宽电压范围内测试了NAND;一些由工厂标记为坏的区块可能在一定的温度或电压条件下仍然能工作,但是,将来可能会失效。如果坏块信息被擦除,就无法再恢复。

/6

/6

文章评论(0条评论)

登录后参与讨论