STN-LCD驱动控制芯片的界面只需要4条信号线,分别为/CS、DATA、/RD和/WR线。其中, /CS线是片选信号。如果/CS的值设为高电平,MCU与STN-LCD驱动控制芯片通信无效并初始化。 送出模式指令或转换模式之前,/CS信号需要一个高准脉冲初始化芯片的串行接口,然后对 芯片发送读写命令时将/CS 设置为低电平。DATA线代表串列数据输入/输出线,所有想要读 取或写入的数据都必须经过DATA线。而/RD线是用来输入READ时钟的,在/RD信号处于下降沿 时,从LCDRAM读出的数据会出现在DATA线上,直到/RD信号出现在下一个下降沿或是/CS的值 变成“1“为止。在/RD信号进入下一个下降沿之前,出现DATA线的数据可以被读进STN-LCD 驱动控制芯片。至于/WR线是用来输入写时钟,在/WR信号处于上升沿时,DATA线上的数据会 写入STN-LCD驱动控制芯片内。另外,如果DATA不需要读回来的话,其实界面只要三条信号 线即可。

3.2 STN-LCD驱动控制芯片部分时序图和Modelsim部分仿真实现

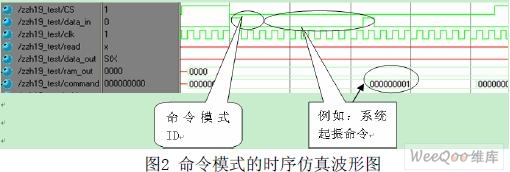

STN-LCD驱动控制可用软体配置,有两种模式的指令可以配置STN-LCD驱动控制的工作模 式和传送LCD 所显示的数据对应不同的ID码。模式设置采用命令模式指令的ID 为100,命令 模式指令包括系统配置指令、系统频率选择、指令LCD 驱动方式、测试模式等等。另一种模 式是数据操作指令由读、写、读-修改-写各项操作构成,该模式的ID分别为110和101。其 中命令模式指令应在数据或数据操作指令发送之前发出。若连续发送命令模式指令,它的标 识码100可省略。当系统工作在非连续接受命令指令或非连续的地址数据方式时,片选信号 /CS应设置为高电平,先前设置的工作模式都复位。一旦片选信号/CS回到低电平,应再发送 一次新的指令标识码。

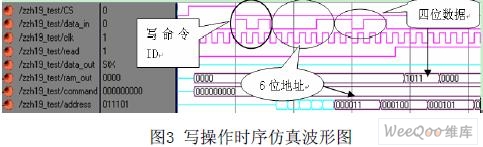

针对前端控制时序模块,在芯片的功能验证中, 我们采用了Verilog 硬件描述语言, 对 电路的逻辑功能和时序关系进行了仿真验证。由于篇幅的限制,所以给出Modelsim部分仿真 实现。

1)命令模式(ID:100)

2)写操作(ID:101)

3.3 命令译码模块(PLA)

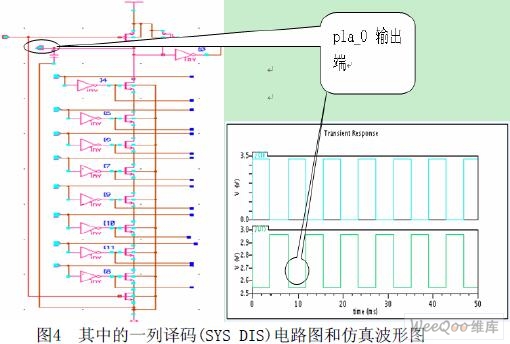

该模块是LCD驱动芯片的控制中心,用以区分数据与命令,并解释输入指令的功能。该 模块在接收到MCU输入的命令后,先进行解释并向相关模块发出控制信号,由后者完成指令 执行,实现指令的可编程。译码器的作用为将外部输人的指令转换为一定宽度的低脉冲信号, 由此低脉冲信号触发相应的电路,改变其状态,实现各项功能。以命令SYS DIS(LCD偏置发 生器停止工作)为例,对应八位数字命令为00000000,将这八个变量经过取非后加上原变量 共有16个变量送入PLA,有且只有PLA-SYS DIS这条线所在的列会产生一个通路,于是PLA-SYS DIS输出低电平,其他的列仍然维持高电平,这样就保证了每次只译码一条命令,就可以配 置好芯片。译码器采用NMOS 与非阵列结构, 来自M CU 的指令代码通过专用芯片的接口模块 电路产生9位输入信号,设计中的指令为8位,最后一位为无关位即第9位是为了指令扩展用。 但在没有扩展之前,对于PLA指令译码电路来说,在8位数据暂存起来后,必须取消第9位移 入PLA。否则会发生错误的译码。其中的一列(SYS DIS)译码电路如下图4所示。

3.4 seg和com驱动电路设计

该模块的输入通过与命令译码模块输出的信号,时钟信号连接,控制1/2、1/3偏置选项 和几种偏压值。也是专用芯片与液晶显示器的接口,其作用是提高驱动能力、实现偏压显示、 实现偏压极性的交流转换。它包括com 驱动器、seg 驱动器及com的移位寄存器。seg驱动器 向液晶显示器提供显示数据;com驱动器向液晶显示器提供行扫描信号。在com 和seg 的配 合下,实现RAM 矩阵内容的液晶显示。com驱动电路原理与seg驱动电路原理类似,它只需电 路满足在不同占空比(扫描行数为n,占空比1/n)下输出相应的周期性行扫描波形。图5为 seg驱动电路仿真结果。

/1

/1

文章评论(0条评论)

登录后参与讨论