上一篇日志给出了关于流水灯的代码,这篇文章介绍一下如何对其进行仿真。

仿真工具:ModelSim

1、双击ModelSim图标,打开ModelSim;

2、点击File->New->Project;创建一个工程,取名LED_test,接着点击Browse,选取工程所存放的位置;最后点击OK;

3、这是将会弹出一个对话框,我们暂时不管它,把它关掉;

4、在工程标签的空白处点击右键,选择Add to Project->Existing File,将我们的要仿真的文件添加进去;其实上面我们关闭的对话框也是执行相同的功能;

5、在工程标签的空白处点击右键,选择Add to Project->New File,取名LED_test,创建一个新的的Verilog文件,然后将下面这段代码添加进去;

`timescale 1ns/1ns

module LED_test();

reg rst_n,clk50M;

wire[9:0] led;

LED u1(.rst_n(rst_n),.clk50M(clk50M),.led(led));

//产生复位信号

initial

begin

rst_n=1'b1;

#20 rst_n=1'b0;

#60 rst_n=1'b1;

end

//产生时钟信号

parameter clk_period=4'd10;

initial

begin

clk50M=1'b0;

forever #clk_period clk50M=~clk50M;

end

endmodule

上面这段代码就是所谓的测试平台(testbench);

6、继续在工程标签的空白处点击右键,选择Compile->Compile All,这是可以看到工程面板的状态一栏两个文件都打上了勾;

7、双击LED_test.v,这时将出现一个叫做object的窗口,在其空白处点击右键,在弹出的菜单中选择Add to Wave->Signal in Design,这时候就会出现波形窗口了;

8、在菜单栏选择Simulte->Run->Run,这是将默认运行100ns;

9、在下面Transcript栏中输入run @ 1000000,这时候仿真就会运行1000000ns,注意run 1000000和run @ 1000000命令是有区别的,前者是在原来的基础上接着运行1000000ns,后者是仿真就运行到1000000ns;

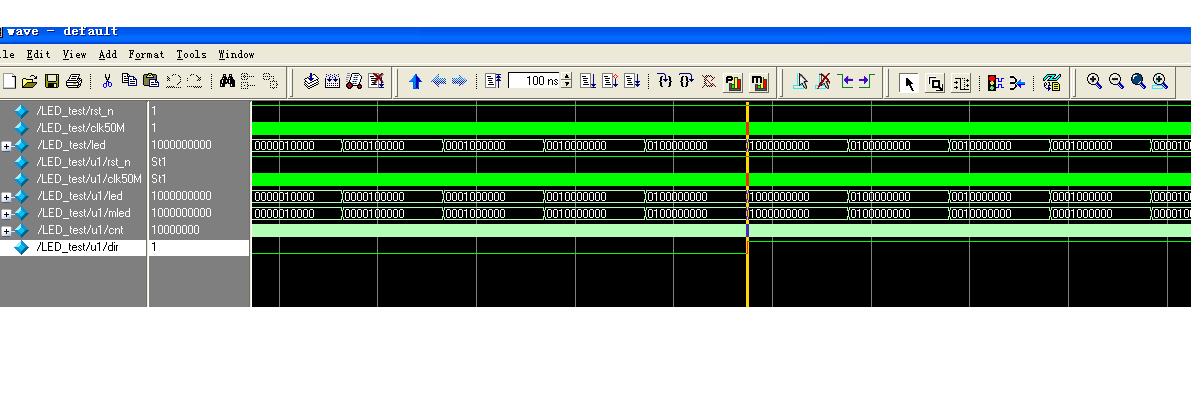

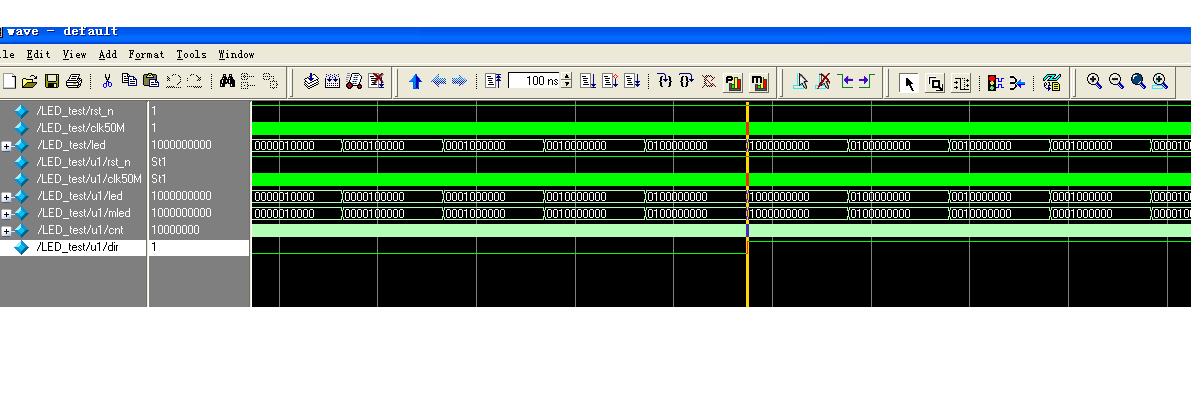

10、下面是上一篇日志第一种代码的仿真波形,为了缩短仿真时间,将reg[23:0] cnt改为reg[7:0] cnt,当然下面也要做相应的修改,这里就不啰嗦了。

/5

/5

文章评论(0条评论)

登录后参与讨论