Tune Matching 的方法有許多,有利用單獨供電給 PA,直接在 Active 情況下 Tune Matching 的方式[1],但是這方法要有兩個條件 :

1. 能够正常通话

2. 能进入非信令模式

然而 Tune Matching 的工作,多半都是在第一版 PCB 就要完成(因為第二版 PCB 就要直接送認證),但是依個人經驗,通常第一版 PCB,軟體可能尚未 Ready, 正常通話 ? 进入非信令模式 ? 再等等唄。

因此個人較偏好利用 Passive 方式 Tune Matching,你只要有板子就能進行,不必等到軟體 Ready。

由於 GSM ? WCDMA 是手機的核心,故個人以這兩個功能的 Tx/Rx Matching 來 做說明。

最理想情況,當然是希望 Source 端的輸出阻抗為 50 歐姆,傳輸線的阻抗為 50歐姆,Load 端的輸入阻抗也是 50 歐姆,一路 50 歐姆下去,這是最理想的。

但是,板廠的製程,在 Trace 的線寬,以及對地間距,一定會有誤差,這導致 Trace 的阻抗,未必是 50 歐姆,所以要靠Matching 把阻抗 Tune 到 50 歐姆。所 以通常就算對於阻抗控制再有信心,也會留 Dummy pad,以備不時之需。

先把落地元件拔掉,串聯元件用 0 歐姆電阻,目的是要知道 PCB Trace 最原始的 阻抗為多少,接下來才能利用 Smith Chart ? Matching 元件,把阻抗 Tune 到 50 歐姆。

Q. 我可以直接用焊錫 Short,來代替 0 歐姆電阻嗎 ? 這樣比較省事。

答案是不行,因為雖然以電路觀點,都是 Short,但是以高頻觀點,利用焊錫這種 Distributed 方式,會有寄生效應,連帶使得你量出來的阻抗會不準。

零件換好後,先把網路分析儀做校正,再將銅管作 Port extension,如此便可 開始量阻抗。

我們發現 PCB Trace 最原始的負載阻抗為(40.6-13j)歐姆,接下來就是利用 Smith Chart,將負載阻抗 Tune 到 50 歐姆。

也就是要把負載阻抗,依序透過 Z1, Z2, Z3,把阻抗由(40.6-13j)歐姆,Tune 成 50 歐姆。

首先要把阻抗,弄到通過 50 歐姆的 Z-plane/Y-Plane 圓周上,也就是下圖兩個藍 色圈圈的圓周上,

而下圖是串電感、串電容、並電感、並電容的軌跡。

因為 Z1 是落地元件,所以透過並聯方式,將阻抗弄到通過 50 歐姆的 Z-plane/Y-Plane 圓周上。

但是我們發現,不管是並電感,

或是並電容,

其阻抗都跑不到我們要的圓周上,因此 Z1 就直接 Dummy。依此類推,若往後 遇到 T 型 Matching,Z1 為串聯元件,但串電容?串電感都跑不到我們要的圓周 上時,這時 Z1 就放 0 歐姆。

而 Z2 是串聯元件,利用串 9.8nH 的電感,將阻抗弄到了我們要的圓周上,此時 阻抗為(40.4 + 19.3j)歐姆。

最後 Z3 又是落地元件,因此並一個 3.1pF 的電容,使阻抗跑到(49.7 + 0j)歐姆。

因此我們利用串 9.8nH,並 3.1pF 的組合,將負載阻抗由原始的(40.6-13j)歐姆, Tune 成了 49.7 歐姆。

Q. 如果我阻抗控制作的相當好,不需任何 Matching 元件就有 50 歐姆,我可以 在下一版 PCB 拿掉這些 Matching 元件嗎 ?

答案當然是可以,好處有三:

1. 減少零件,便可 Cost Down

2. 減少零件,降低 SMT issue 的風險

3. 減少零件,降低 Insertion Loss

第 3 點對於 GPS 尤其重要,我們由 Noise Figure 的公式 :

發現 GPS LNA 前的 Noise Figure,幾乎決定了整體電路的 Noise Figure。

換句話說,若 LNA 前的 Noise Figure 不好,那麼 C/N 值? Sensitivity,注定不會 好,因此要想辦法將 LNA 前的 Loss 降到最低。而 Loss 來源有二 :

1. Mismatch Loss

2. Insertion Loss

若阻抗控制得相當好,等同於幾乎沒有 Mismatch Loss,若能將這些 Passive 的 Matching 元件拿掉,便可更進一步降低 Insertion Loss。即便是 0 歐姆電阻,仍 有些微的 Insertion Loss,更何況 GPS 接收的是-150 dBm 極微弱的訊號,些微的 Insertion Loss,對於 C/N 值? Sensitivity,已有相當的影響。因此若阻抗控制作 的相當好,建議下一版 PCB 就直接用 Microstrip 連過去。

至於 Matching 的原則,一般而言有五項 :

1. 電感/電容值,不要過小

2. 落地電容值,不要過大

3. 電感/電容值,不要過於冷門

4. 盡可能設計成 Low Pass Filter

5. 整個頻帶的阻抗軌跡盡可能收斂

電感/電容值之所以不要過小,原因是要維持 Matching 的穩定性,因為 電感/電容值會有誤差,以電容為例子,差不多會有正負 0.1pF 的誤差,如果是 一個容值為 0.3pF 的電容,則誤差高達 33%,其容值範圍為 0.2pF ~ 0.4pF,這 可能會導致每片 PCB 的 Tx/Rx Performance 不一致,進而影響工廠量產時的良率。

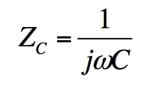

落地電容值之所以不要過大,是因為依照容抗公式 :

電容值越大,容抗越小,因此落地電容值過大,則反而可能會讓訊號都流到 GND。

電感/電容值,不要過於冷門,原因是方便備料,因為若是常見的值,則所有廠 家都會有,量產過程中,若 First Source 的廠家缺料,還可馬上找 Second Source 的廠家。

原创文章,转载请注明: 转载自 吴川斌的博客 http://www.mr-wu.cn/

本文链接地址: 天线匹配电路–来至台湾省的工程师的心水总结–不敢独享 http://www.mr-wu.cn/antenna-tuning-and-matching/

/5

/5

文章评论(0条评论)

登录后参与讨论