TI公司的LM3S811有3个PWM信号发生模块,每个模块可以产生2个独立的PWM信号,这样算来,单个LM3S811就可以产生6路PWM信号了。

对于有些应用,对成本有要求,用R,C替代专用DAC毕竟能节约不少,尤其在精度要求不高,电平变化速率不快的应用中,就可以通过PWM滤波后产生直流信号,但这样生成的信号达到什么指标呢。自己先定一个指标吧,看能不能达到。上一篇《LM3S811之测量交流有效值》在10v的量程下可以测量到10mv的精度,约10位分辨率,现在还是用这个芯片,生成的信号比测量的信号精度高一位吧,这样比较合适。比如是3.3v量程,分辨率是3.3/2^11=1.6mv。

下面几张图供参考,尊重作者,不重新画了。

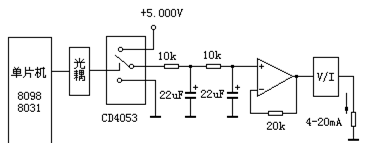

图1来自 李小京,石金桥《利用单片机构成高精度PWM式12位D/A》

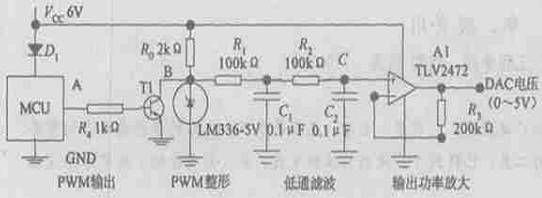

图2来自 秦健《一种基于PWM的电压输出DAC电路设计》

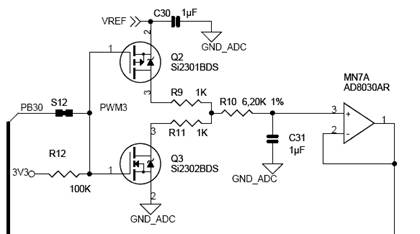

图3来自 Atmel评估板原理图

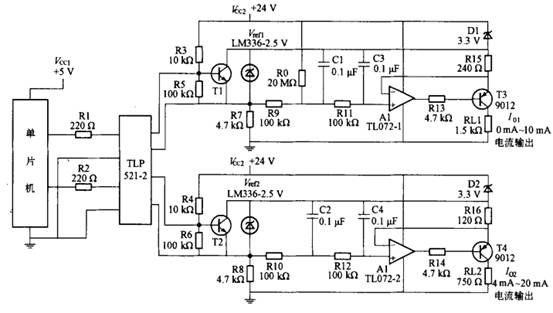

图4来自 韦波《用PWM实现廉价隔离型标准电流输出D/A转换器》

从PWM数字信号变为产生DAC模拟信号,一般都是分几步走:

一:利用LM3S811产生PWM信号,这块属于数字电路,不讨论了。

二:PWM信号整形/隔离,顾名思义,由于数字电路芯片输出的高电平和低电平不稳定,随着温度的变化而变化,而整形可以采用高速光耦、晶体管、运放/比较器.图1-3都比较简单,但可能存在问题,以图2为例,我用软件仿真后,占空比经过T1后反了可以在软件中修改,但B点的方波,低电平是26mv,对于C点,最低电压是31.8mv,相对于1.6mv比较大了,图4则可以降低到0v。当然用运放/比较器肯定也会达到0v的。

三:滤波,将方波整形成直流信号。这个是重点,也是难点,滤波器,精度与时间是一对矛盾。

一般电路都有两种分析方法:从频域上分析和从时域上分析。大部分文档都是从频域上分析的,参考秦健《一种基于PWM的电压输出DAC电路设计》

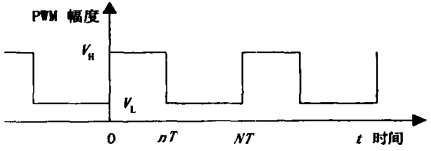

图5 PWM波形

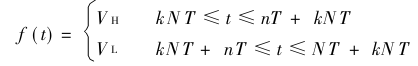

可用公式 描述,频域上用傅里叶级数表示

描述,频域上用傅里叶级数表示 ,通过低通滤波器后,主要考虑的是一次谐波的影响,再后面的谐波影响加起来都小于一次谐波的影响。

,通过低通滤波器后,主要考虑的是一次谐波的影响,再后面的谐波影响加起来都小于一次谐波的影响。

一次谐波的频率是2*pi/NT,以LM3S811为例,最小计时应该可以达到50MHz,16位PWM计数器完全满足11位的精度,N=2^11=2048。留点余地以后扩展也好,波形更加方也好,计时4个50M的脉冲算最小分辨率吧,这样一个NT为2048*4/50M=163.84us。则一次谐波的频率为2*3.14/163.84u=38.35kHz。

如果要将一次谐波的影响消除到1/2^12,即低通滤波器必须在38.35kHz时,以其极限VH=3.3v,VL=0V,n=N为例,其频率响应的电压增益要为20lg(2/pi/2^12)=-76.17db以下。

以一级RC低通滤波器为例,其截止频率为1/2*pi*RC,则20lg(1/2*pi*RC)=-76.17,则1/(2*pi *RC)=10^(-76.17/20),很显然即便是1M的电阻,1u的电容组成的单级滤波器都达不到这个效果。

多级RC滤波器计算比较复杂,但可以以上面几张图中的100k,0.1u的为例,其单级的-3db频率为1/2*pi*100k*0.1u=15.9Hz,则在38.35KHz单级幅度则为衰减到1/(38.35k/15.9)=1/2412 了,若要达到1/2^12,则需要2^12/2412=1.7,则采用2级RC滤波器可行。但在没有采用运放隔离的情况下,两级RC滤波器会前后干扰,前级的输出为后级的输入,后级的输入为前级的负载,则第一级采用10k,1u,第二级采用100k,0.1u,-3db频率一样,但干扰就相对降低了。

频域上可以分析保证纹波不超过规定,但无法分析时间关系了。

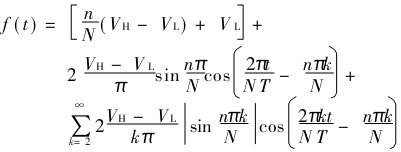

由于多级RC电路函数关系比较复杂,仅以单级RC电路为例。从时域上分析,借用下图,其电压的函数关系也类似,a)是充电,b)是放电,以充电为例,Vc=V(1-e^(-t/RC))。要达到2^-12的精度,极限就是从0V到V*8191/8192,算得t=9.02RC,简单点就是10RC肯定就满足稳定的要求了。如果R=100k,C=1u,则最大只需要1s即可稳定。至于100k,0.1u、10k,1u,那0.1s就可以稳定了。

图6 RC电路的时域函数图

时域上也可以分析纹波吧,常见图5,一个周期是164us,在极限的情况下,即图6a)从0点开始,其纹波是V(1-e^(-164u/100k/1u))=0.0016V,呵呵,那就超出了V*2^-12=0.0002V了。如果要纹波系数小,必须减小T或增大RC,当然,减小T是比较容易的,最小可以2^11/50M=41us,这样纹波就是V(1-e^(-41u/100k/1u))= 0.0004V,呵呵,单级的还是不行啊,除非降低标准,分辨率降低到10位,同时T又能减小,哦,那肯定满足了。

综上所述,采用2级RC滤波器,10k,1u和100k,0.1u,稳定时间约0.1s,可构成11位精度的DAC,对于一般应用,足矣。

四:输出功率放大

最常用的是用运放构成电压跟随器,我想如采用三极管射级跟随,既能降低成本,也能向下平移电压约0.7V,这样图1,2,3就可以达到0V的目的,但温度稳定度可能还不够,我只是想想了。

费这么多力气,算了半天,讨论了PWM模拟DAC,其实主要还是想利用LM3S811做个SOC,理论上先论证下可行性,看样子还是可以的。

/5

/5

用户377235 2012-8-29 11:19

用户377235 2012-8-1 12:37

支持

用户306131 2012-4-11 19:54

试了一把过程如下:逻辑部分编译完后,下载sof文件,然后去nios里打开调试,这样就可以调试nios部分了,如果在nios里某些信号改变会影响逻辑部分,然后你又想看逻辑部分接受到nios发出的信号而发生的某些改变的话,就首先得在逻辑部分添加signalTap,把需要的信号都添加进去,选择nios部分可以改变某个信号的触发方式,编译一把,把这些仿真信息也综合进去,然后和上面一样,下载sof,然后去nios部分调试,当某个逻辑部分用到的信号改变了以后,由于前面已经选择了此信号触发了,所以会在signalTap出来此条件触发后相应的时序图。

用户403664 2012-4-11 08:52