一、概述

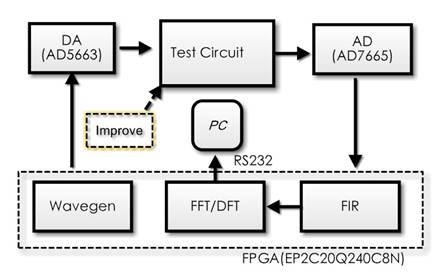

设计以FPGA(EP2C20Q240C8N)作为主要控制芯片,通过DA转换器AD5663给被测的运算放大器施加频率可调、幅度可调的激励信号源,经过运算放大器之后,再通过DA转换器AD7665,将采样数据在FPGA中进行滤波和谐波分析,最后将谐波的数据通过RS232串口上传到PC机,通过上位机对谐波进行分析,得出出现失真的主要原因。然后根据失真的主要原因施加相应措施实现对运算放大器THD参数的优化。

二、分析与设计 (一)分析运算放大器的THD参数(Total Harmonic Distortion,总谐波失真)是放大器非常重要的指标之一,用以表征信号在通过放大器时被叠加的额外谐波分量的多少(本例中仅考虑2次和3次谐波)。根据设计要求,课程设计如图1所示。

图1 整体框图

系统中使用FPGA作为主要的控制器,在FPGA内部主要分为五部分,WaveGen、AD、FFT/DFT、FIR和RS232串口通讯。其中,WaveGen部分主要是给测试的运算放大器施加频率可调、幅度可调的激励信号源。AD部分主要是将AD7665采样回来的数据进行处理。FIR部分是对采样数据进行低通滤波处理,滤除信号中的误差信号。FFT/DFT部分是将数据进行谐波分析,分析出二次和三次谐波,将最终的谐波信号通过通信RS232串口上传到PC上位机,完成整个测试。然后上位机通过谐波信号得到信号失真的主要原因,根据原因施加改善措施,实现常用运算放大器的THD参数测量及优化。

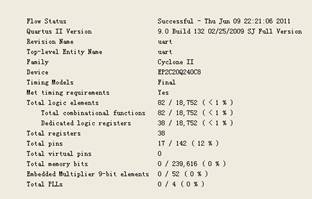

因为课程设计中,FPGA作为主要的控制器,而FIR和FFT/DFT需要占用很多FPGA内部的逻辑单元,需要在选择FPGA时,选择内部资源较多的芯片。综合考虑芯片的逻辑资源量、最大存储量、最大时钟频率、I/O引脚数、集成度及价格等因素,本设计采用Altera公司Cyclone II 系列中的具有240个引脚封装的EP2C20Q240C8N,保证片内的资源足够课程设计使用。

它主要具有如下特性:

186752个逻辑单元; 52个M4K嵌入式存储器模块; 240Kb的RAM总容量; 4-1"PLL锁相环; 26个嵌入式18x18乘法器; 315个用户可用引脚。其I/O口可分为8个I/O Bank,每个Bank可根据需要配置1.2或3.3伏的电平来与外围硬件电路连接。

2.AD转换器的选择在选择AD转换器是主要考虑两个方面,转换的精度和数据传输的速度。数据的转换的精度主要保证采样时保证信号的完整性,但是AD采样必然导致采样误差的存在,精度越高的AD误差越小,为了保证设计中的误差范围,需要保证AD采样的精度在16位以上。数据传输的速度上面,是为了保证采样的数据能够及时准确的传回FPGA内部,采样精度越高,需要的数据传输率就越高,因此数据传输率必须要在400ksPs以上才能保证要求。

经过综合考虑最后选择AD7665作为AD转换器。其中,AD7665 的主要特点:

吞吐量,570 kSPS(Warp模式)、500 kSPS(正常模式) 16位分辨率、无失码 模拟输入电压范围:DA转换器的选择需要保证转换的速度,最后选择AD5663作为主要的DA转换器。主要技术参数如下:

低功耗、双通道、16位nanoDAC 相对精度:±12 LSB(最大值) 10引脚MSOP和3 mm × 3 mm、LFCSP_WD封装 采用2.7 V至5.5 V电源供电 各通道独立省电 上电复位至零电平或中间电平 硬件LDAC和CLR功能 串行接口,时钟速率最高达50 MHz 三、仿真设计仿真设计中,主要是对RS232部分进行了程序的编写、仿真、下载以及硬件调试。串口主要是工作波特率在9600,主要包括发送和接收两部分。主要仿真图像如图2所示:

图2 RS232仿真图(发送两组数据,接收)

通过仿真可以发现,串口工作基本正常。在quartusII里面建立EP2C20Q240 C8N芯片的工程,运行建立相应的下载程序。运行时间戳如图:

图3 quartusII工程运行时间戳

下载到FPGA中,运行的页面:

图4 串口调试

四、硬件电路设计 (一)电源部分的设计电路板主要使用5V供电,数字部分的供电主要包括给FPGA的1.2V和3.3V,模拟部分的供电通过输入的5V经过LT1935DC然后稳压到+5V和-5V,在模拟部分使用了REF3040产生4.0V的基准电压,给模拟部分提供准确的基准电压。电源部分的电路如图5所示。

图5 电源部分电路

(二)AD部分所使用的AD7665具有强大的功能,在数据传输方面支持并口和串口两种方式,为了减少走线的复杂度,电路使用串行通信的方式,主要电路如图6所示。

图6 AD电路

(三)DA部分使用DA5663可以同时产生两路DA输出信号,将输出的两路信号进行叠加,主要电路如图所示。其中,AD和DA部分的供电全都使用模拟供电,REF使用的4V为主要基准,可以减少在电路调试过程中产生的误差。

图7 DA电路

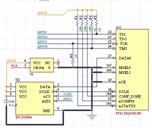

(四)FPGA部分电路通信中主要占用了FPGA (EP2C20Q240C8N)的BANK8的接口,因为AD转换器和DA转换器均采用的是串口通信,占用的IO口较少,节省了很多资源,减少了走线的复杂度。

图8 FPGA电路

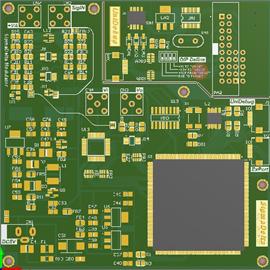

(五)实际电路系统使用的是工厂制作的两层PCB板,在实际制作之前,需要将电路在PCB电路辅助软件Altium Designer中将电路的原理图以及PCB图设计完成,需要根据各个器件的尺寸、特性以及之间的连接线设置好,严格控制板子的总体大小,最后详细的板图如图9。具体硬件电路如图10所示。

图9 详细的板图

图10 硬件电路

此次设计中使用的软件版本为Altium Designer 8,是在行PCB布板的软件版本中使用最广之一。

五、总 结通过此次课程设计,学到了很多有关电路的硬件设计的知识,并且可以熟练掌握FPGA编程和下载,熟练掌握电路调试过程中的各种调试技巧。但是,此次电路设计中还有没有完成的部分,希望在以后的学习中可以继续深入的研究。

/5

/5

用户367863 2011-7-4 09:30