阻塞赋值和非阻塞赋值是verilog里一个难点,也是重点,相关区别各大论坛博客里都有详细的讲解。

先说几个经验上的要点。

在时序逻辑里都采用非阻塞赋值,在组合逻辑里采用阻塞赋值,组合时序都存在的块里都采用非阻塞赋值。

但这个并不是死的,我就遇到了这样的问题。

在有for循环的时序逻辑里必须用阻塞赋值!

在做一个把ds18b20测出温度转换成bcd码通过数码管显示的模块中,

2进制转4位表示一个10进制数bcd码,采用加3移位处理,这中间需要进行若干次循环移位,判断。

自然就用到了for语句。起初并没在意,只是用以往的时序逻辑里的非阻塞赋值。

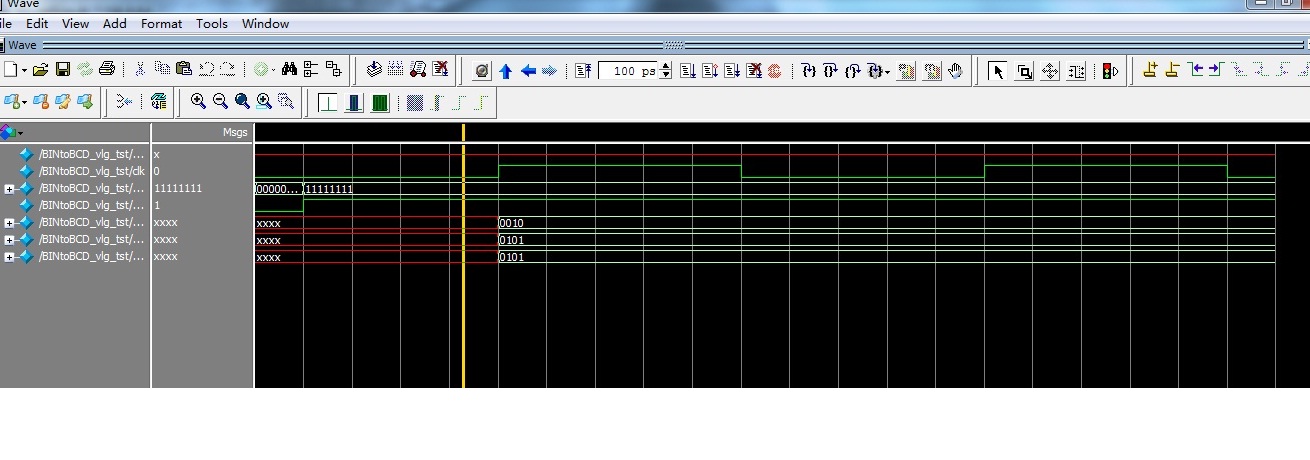

仿真结果另我大跌眼镜,输出数据连续的不定值x,重复检查,揣测后,顿悟。

非阻塞赋值只在整个语句结束后才改变等式左端的值!所以不管for循环几次,用非阻塞赋值,只进行一

次,也就是仿真出现的循环中的不定值。

重新改成阻塞赋值后,结果正确。

前人的经验很重要,但任何事物都要具体问题具体分析!

放上阻塞赋值后的仿真图,非阻塞赋值的错误仿真忘了截了,有兴趣的童鞋可以自己尝试验证。

/5

/5

文章评论(0条评论)

登录后参与讨论