//数码管简单显示

//8个数码管,前4个固定显示1,2,3,4.。后四个的前三个显示1,2,3.最后一位循环显示1-4(1hz)

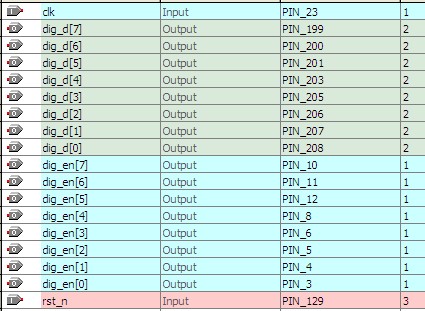

module seg(

input clk,

input rst_n,

output [7:0] dig_en,//数码管低电平使能(vhdl中用的是sacn)

output [7:0] dig_d//七段数码管,最高位 D0 任意

);

//1.分频,设定数码管扫描速度。以及数字变化速度。分别为1khz和1hz

//1khz分频 50_000KHZ 50000/2-1=24999时翻转 2^15=32768

reg clk1khz;

reg [14:0] cnt1;

always @ (posedge clk,negedge rst_n)

if(!rst_n) begin

cnt1<=15'd0;

clk1khz<=1'b0;

end

else if(cnt1==15'd24999) begin

cnt1<=15'd0;

clk1khz<=~clk1khz;

end

else

cnt1<=cnt1+1'b1;

//1hz分频 50_000_000 /2 -1=24_999_999 2^25=33_554_432

reg clk1hz;

reg [24:0] cnt2;

always @ (posedge clk,negedge rst_n)

if(!rst_n) begin

cnt2<=25'd0;

clk1hz<=1'b0;

end

else if(cnt2==25'd24999999) begin

cnt2<=25'd0;

clk1hz<=~clk1hz;

end

else

cnt2<=cnt2+1'b1;

//显示方式

//先写一个在1hz的频率下的计数器(1-4)

reg [2:0] add;

always @ (posedge clk1hz,negedge rst_n)

if(!rst_n) add<=3'd1;

else if(add == 3'd4) add<=3'd1;

else add<=add+1'b1;

//再写个扫描速度,用1khz的计数器控制,共8个数码管,所以计数从0到7

reg [2:0] scan;

always @ (posedge clk1khz,negedge rst_n)

if(!rst_n) scan<=3'd0;

else if(scan == 3'd7) scan<=3'd0;

else scan<=scan+1'b1;

//开始显示

//先写使能控制

reg [3:0] data;

reg [7:0] dig_en_r;

always @(scan) begin //数码管使能从右到左(代码从上到下)

case (scan) //0使能

3'd0 : begin data<=add; dig_en_r<=8'b11111110;end// dig_en0

3'd1 : begin data<=4'd3;dig_en_r<=8'b11111101;end//

3'd2 : begin data<=4'd2;dig_en_r<=8'b11111011;end//

3'd3 : begin data<=4'd1;dig_en_r<=8'b11110111;end//

3'd4 : begin data<=4'd4;dig_en_r<=8'b11101111;end//

3'd5 : begin data<=4'd3;dig_en_r<=8'b11011111;end//

3'd6 : begin data<=4'd2;dig_en_r<=8'b10111111;end//

3'd7 : begin data<=4'd1;dig_en_r<=8'b01111111;end//dig_en7

default:begin data<=4'd0;dig_en_r<=8'b11111110;end

endcase

end

reg [7:0] dig_d_r;

always @ (data) begin //也是从g-a共阳 0表示亮,1表示灭

case(data)

4'd1 : dig_d_r<=8'hf9;//

4'd2 : dig_d_r<=8'ha4;//

4'd3 : dig_d_r<=8'hb0;//

4'd4 : dig_d_r<=8'h99;//

4'd0 : dig_d_r<=8'hc0;

default:dig_d_r<=8'hc0;

endcase

end

assign dig_d = dig_d_r;

assign dig_en= dig_en_r;

endmodule

总结:

1.

2.

3.代码注意事项:case...default..endcase语句中,begin..end的应用。。。很郁闷。。。有点儿繁琐,verilog为什么会有这么多人用,个人感觉VHDL挺好的。。。

可能大家都学C吧

/5

/5

文章评论(0条评论)

登录后参与讨论