06/18/11 11:00:05 PM

最近一段时间在研究IEEE1588-2008精确时间同步协议(PTP)。该协议可以在软件中实现,如果需要提高时间同步的精度,需要硬件的辅助。多家芯片厂商已经提供具备IEEE1588-2008硬件辅助功能的MAC芯片(National Semiconductor, Vittese, Marvell, Broadcom)或集成MAC的SoC芯片(Intel, ST, Freescale, Hyperstone),或者是专用的时间同步芯片(Maxim, Semtech),还有几家IP Core厂商提供可以在FPGA或ASIC中实现的IP Core(MoreThanIP, Ixxat, Oregano System, Hirschmann, IPClock)。

在我们的产品中,硬件辅助功能需要通过FPGA来实现。最开始我们考虑购买一款IP Core和配套的软件程序。后来经过评估,决定自己开发硬件辅助功能,配以开源的PTPd软件实现全部的硬软件功能。

接下来的几周,我会陆续分析上述几家厂商提供的Datasheet中对该功能实现细节和寄存器接口的介绍。由于部分厂商的网站需要用户签署NDA才能提供Datasheet,我拿不到Datasheet也就无法分析其实现细节。

通过分析各家厂商公开的Datasheet,其硬件辅助逻辑实现的功能可以归纳为以下三个部分:

1. 相位、频率可以粗调和精调的高精度实时时间定时器(RTC)。

2. 对PTP报文到达时间的精确捕获(TimeStamping)。

3. 定时触发和秒脉冲信号PPS产生功能。

接下来的分析,主要集中在上述第一个部分。

06/20/11 10:55:14 PM

MPC8315E PowerQUICC II Pro Integrated Host Processor Family Reference Manual

19 Enhanced Three-Speed Ethernet Controllers

19.6 Functional Description

19.6.6 Hardware Assist for IEEE 1588-Compatible Timestamping

19.5 Memory Map/Register Definition

19.5.3 Memory-Mapped Register Descriptions

19.5.3.10 IEEE 1588-Compatible Timestamping Registers

19.5.3.10.1 Timer Control Register (TMR_CTRL)

19.5.3.10.2 Timer Event Register (TMR_TEVENT)

19.5.3.10.3 Timer Event Mask Register (TMR_TEMASK)

19.5.3.10.4 Timer PTP Packet Event Register (TMR_PEVENT)

19.5.3.10.5 Timer Event Mask Register (TMR_PEMASK)

19.5.3.10.6 Timer Status Register (TMR_STAT)

19.5.3.10.7 Timer Counter Register (TMR_CNT_H/L)

19.5.3.10.8 Timer Drift Compensation Addend Register (TMR_ADD)

19.5.3.10.9 Timer Accumulator Register (TMR_ACC)

19.5.3.10.10 Timer Prescale Register (TMR_PRSC)

19.5.3.10.11 Timer Offset Register (TMROFF_H/L)

19.5.3.10.12 Alarm Time Comparator Register (TMR_ALARM1–2_H/L)

19.5.3.10.13 Timer Fixed Interval Period Register (TMR_FIPER1–3)

19.5.3.10.14 External Trigger Stamp Register (TMR_ETTS1–2_H/L)

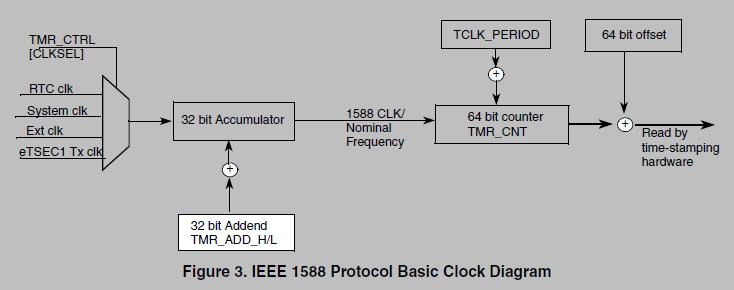

飞思卡尔的PowerPC系列芯片支持Hardware-assisted 1588。在19.6.6功能描述中没有对Timer实现细节和工作原理的介绍,只有对打时间戳功能的介绍。接下来,需要对19.5.3.10寄存器描述中Timer相关的寄存器进行分析。

19.5.3.10.7 Timer Counter Register (TMR_CNT_H/L):64位,定时计数器寄存器。该寄存器与TMROFF_H/L寄存器相加,得到当前计数器值。两次 TMR_CNT_H/L+TMROFF_H/L相加操作的时间间隔,由TMR_ADD和TMR_ACC确定。这样一来, TMR_CNT_H/L递增的步长和周期就都是可控的了。

由于CPU访问总线的时钟与计数器工作时钟工作在两个时钟域,而且计数器时钟频率较高,所以该寄存器的设计需要考虑跨时钟域可靠传递数据的问题,这里采用的是“直接访问影子寄存器,间接访问本体寄存器”的单向握手操作方法。读写操作分别描述如下:

一、读取定时器计数值:第一步读取 TMR_CNT_L低32位寄存器,读取操作引发计数器TMR_CNT_L和TMR_CNT_H当前值同步(计数器时钟域)拷贝到64位影子寄存器,读取值从影子寄存器的低32位得到(CPU时钟域);第二步读取TMR_CNT_H高32位寄存器,读取值从影子寄存器的高32位得到(CPU时钟域)。

二、加载定时器计数值:第一步写入TMR_CNT_L低32位寄存器,仅更新影子寄存器低32位(CPU时钟域);第二步写入TMR_CNT_H高32位寄存器,既更新影子寄存器高32位(CPU时钟域),写入操作还引发64位影子寄存器同步(计数器时钟域)拷贝到计数器,更新TMR_CNT_L和TMR_CNT_H的当前值。

在上面的步骤中,同步拷贝动作的触发可以采用标准的跨时钟域“两级寄存器同步,第三级寄存器边沿检测”方法实现。

19.5.3.10.11 Timer Offset Register (TMROFF_H/L):64位,定时计数器递增步长寄存器。该寄存器周期性地与 TMR_CNT_H/L寄存器相加,更新 TMR_CNT_H/L寄存器当前值。

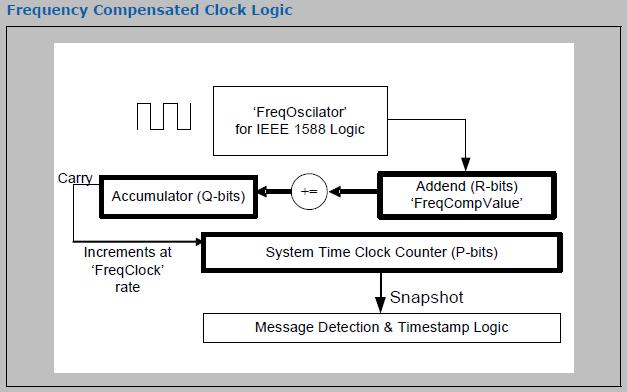

19.5.3.10.8 Timer Drift Compensation Addend Register (TMR_ADD):32位,定时计数器递增周期累加值寄存器。TMR_ADD在每一个计数器工作时钟周期与TMR_ACC相加。

19.5.3.10.9 Timer Accumulator Register (TMR_ACC):32位,定时计数器递增周期累加寄存器。TMR_ACC在每一个计数器工作时钟周期递增TMR_ADD,当其第32位产生进位操作时,进位脉冲触发TMR_CNT_H/L与TMROFF_H/L相加操作。

递增周期累加值寄存器TMR_ADD的计算如下:

TMR_ADD = ceil(2^32/(freqOsc/freqIncr))

其中,ceil()是进位取整运算,freqOsc是计数器工作时钟频率,freqIncr是计数器递增频率。freqIncr的选取应该使freqOsc/freqIncr >= 1.0001。

递增步长寄存器TMROFF_H/L的计算如下:

TMROFF_H/L = (1/freqIncr)*2^subNanoSecBit

其中,subNanoSecBit是64位定时计数器中用来表示亚纳秒(sub-nano second)时间值的位数。

TMR_ADD的设置,使得freqOsc的精度提高至1/2^32;TMROFF_H/L的设置,使得TMR_CNT_H/L/2^subNanoSecBit计算值的单位恰好为纳秒。

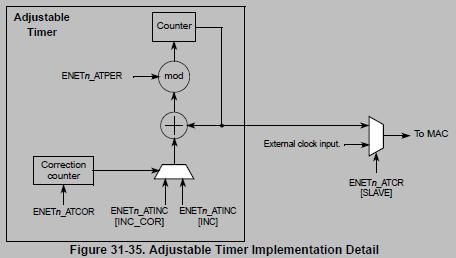

32位定时计数器ENETn_ATVR在每一个时钟周期与7位递增步长寄存器ENETn_ATINC[6:0]相加,更新定时计数器取值。当定时计数器超过32位周期寄存器ENETn_ATPER时,定时计数器从超出值开始重新递增。另一个32位计数器在每一个时钟周期递增1,当其计数值等于调整周期寄存器ENETn_ATPER时,计数器归零,并触发7位递增步长调整寄存器ENETn_ATINC[14:8]代替ENETn_ATINC[6:0]与ENETn_ATVR相加。

其中,ENETn_ATINC[6:0]的设置,使定时计数器的取值恰好以纳秒为单位:

ENETn_ATINC[6:0] = 10^9*(1/freqOsc)

ENETn_ATPER的设置为10^9,使定时计数器超过10^9ns = 1s时翻转,实现“秒定时器”功能,并提供纳秒级时间精度。

当Slave与Master时间相差很大时,可以通过直接写入定时计数器ENETn_ATVR,实现粗调;当Slave与Master时间相差较小时,可以通过设置递增步长调整值ENETn_ATINC[14:8],与调整周期值ENETn_ATPER,以较小的幅度,较大的周期实现微调,逐步逼近Master的时间和频率。

06/23/11 09:02:27 PM

ADSP-BF51x Blackfin? Processor Hardware Reference

STM32F101xx, STM32F102xx, STM32F103xx, STM32F105xx and STM32F107xx advanced ARM-based 32-bit MCUs Reference Manual

Utilizing IEEE 1588 with Intel? EP80579 Integrated Processor Product Line

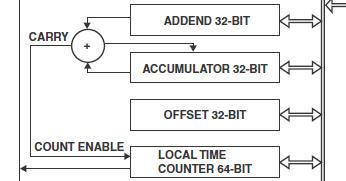

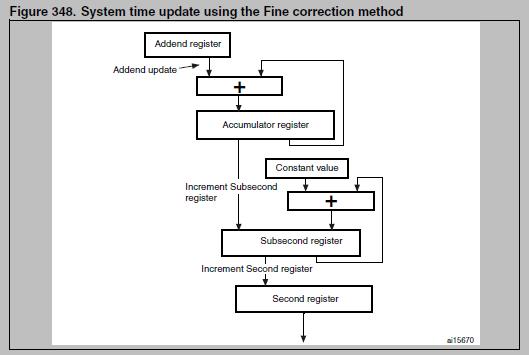

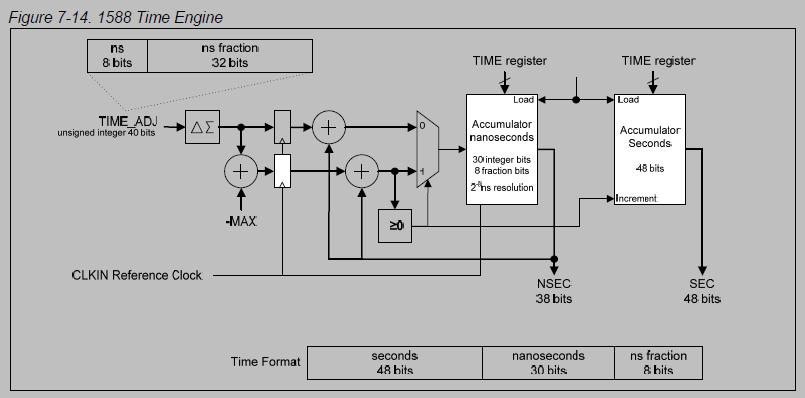

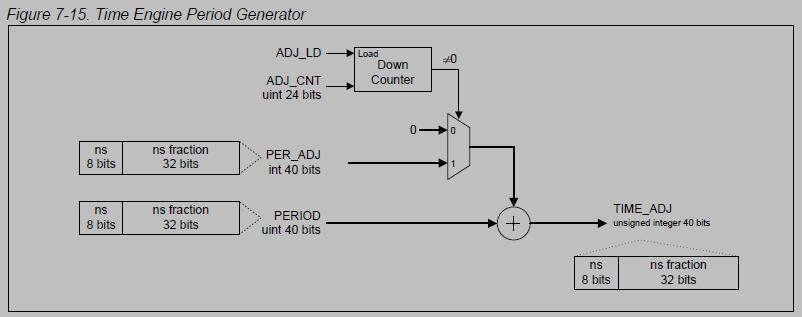

从上述三篇文档可以看出,ADI, ST, Intel三家芯片厂商设计的1588实时时钟电路十分相似,电路的工作原理与FreeScale的PowerPC处理器中的实时时钟电路如初一辙。三家芯片厂商的电路原理图如下:

用户377235 2016-2-17 16:28

用户377235 2015-9-16 04:28

用户377235 2012-12-16 20:25

用户415454 2012-5-31 12:54

用户411257 2011-12-28 15:23

ash_riple_768180695 2011-8-9 21:10

用户1398106 2011-8-3 16:33

用户1492539 2011-6-21 08:29

用户1275742 2011-6-20 17:32