原创

《手把手教你设计CPU——RISC-V处理器篇》一次畅快的学习之旅

首先感谢面包板社区举办这次赠书活动。知道和保持关注RISC-V已经有一段时间了,看到这个活动后,果断提交了申请。很幸运,申请通过了。然而后来由于沟通上的一点问题,主办方没有发书给我,为此有点小失落。幸运的是,评测群里有人因为最近没有时间看书而转让给了我,于是就有了这篇书评。

RISC-V作为一种新兴的开源指令集架构,在发布几年内得到了越来越多的关注,尤其最近两三年发展迅猛,甚至可以说是炙手可热。对于这本书我也闻名已久,这次终于有机会一睹为快。利用业余时间读了七章内容,谈点自己的感受和体会吧。

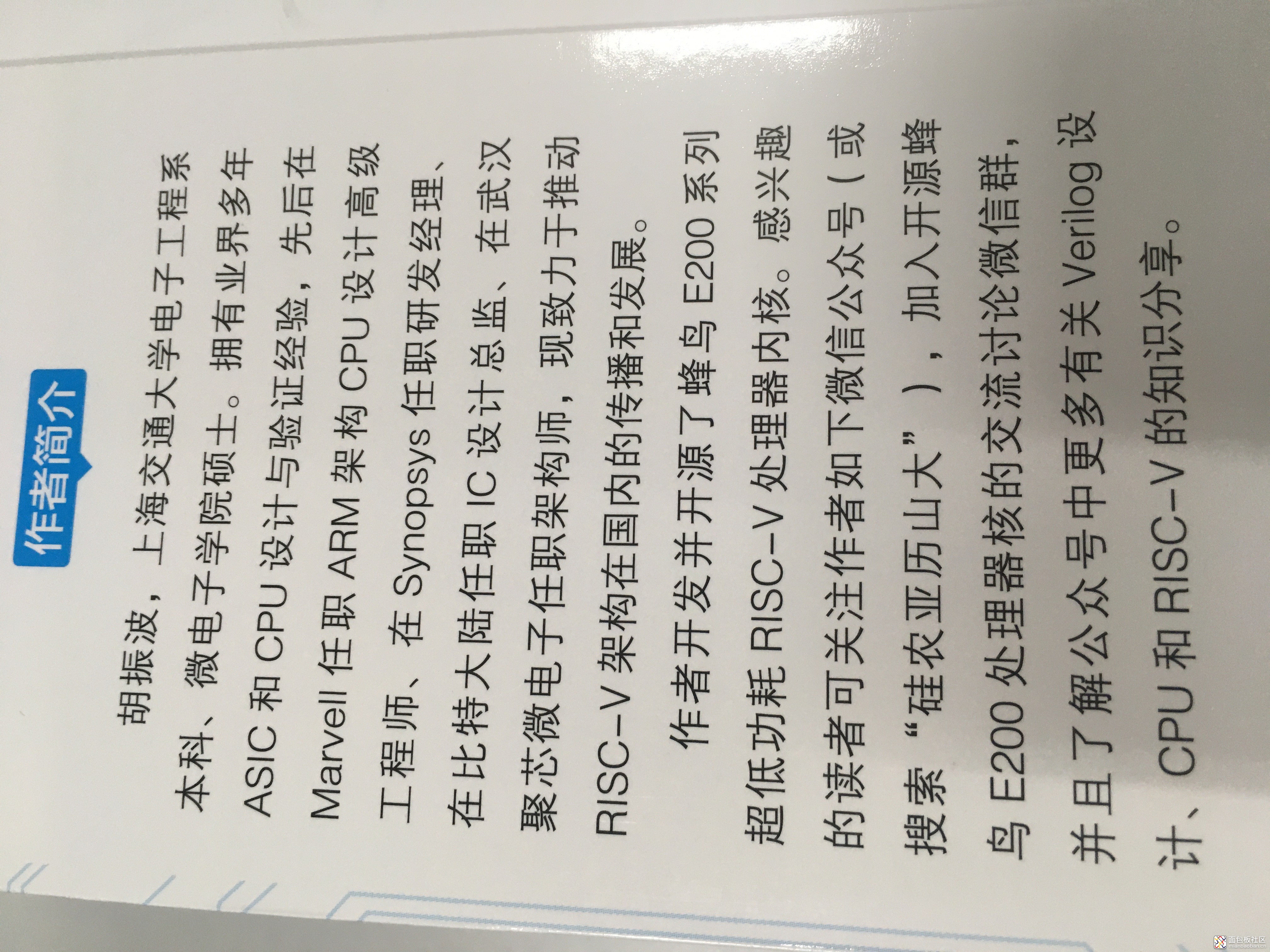

作为一本技术书籍,是否值得一读,是否有最后的吸引力,作者的技术水准是基本保障。本书作者何许人也?看下图:

因此可以说,作者的技术水平是完全胜任这本书的编写的。尤其是作者本人就是开源RISC-V处理器核E203的核心开发者,写本书自然是再合适不过了。

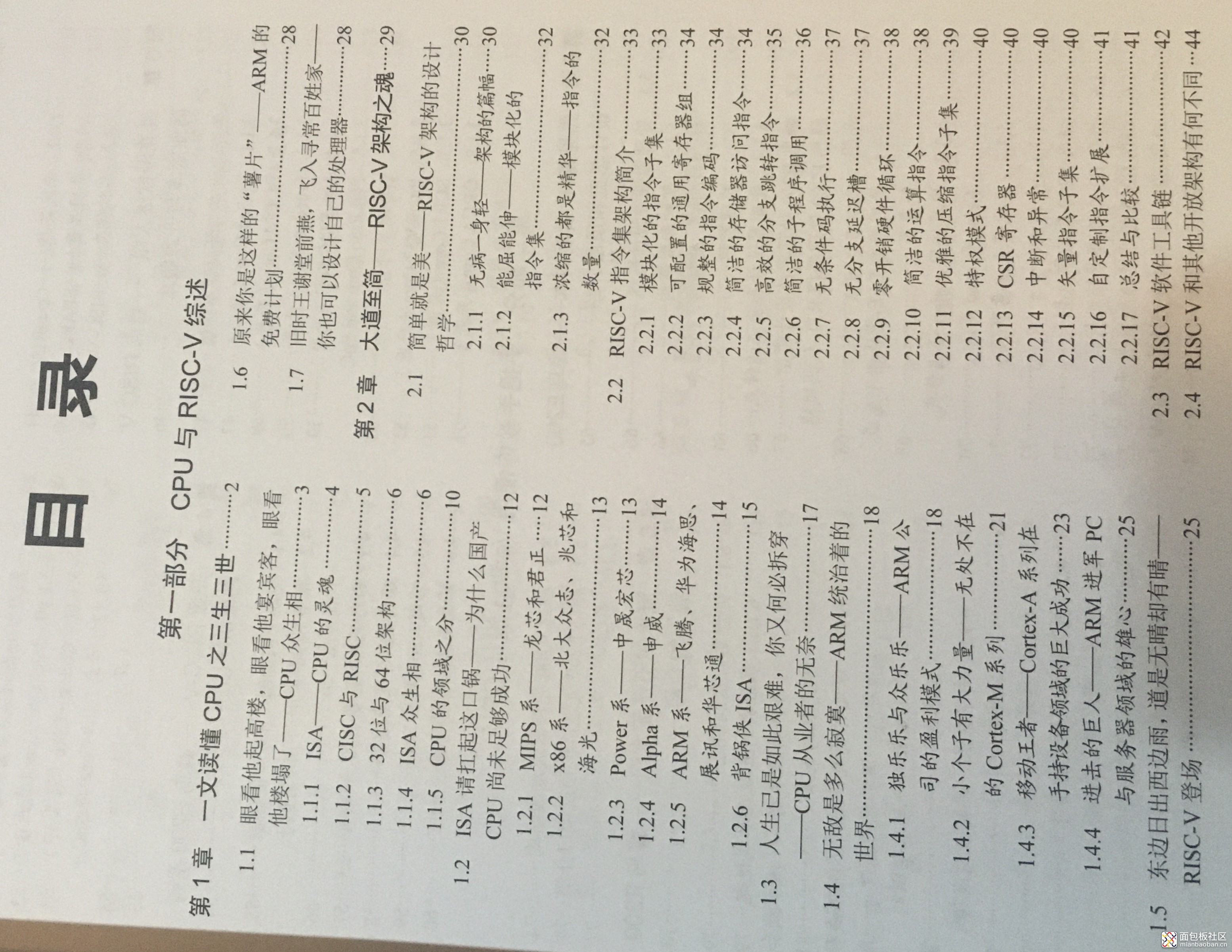

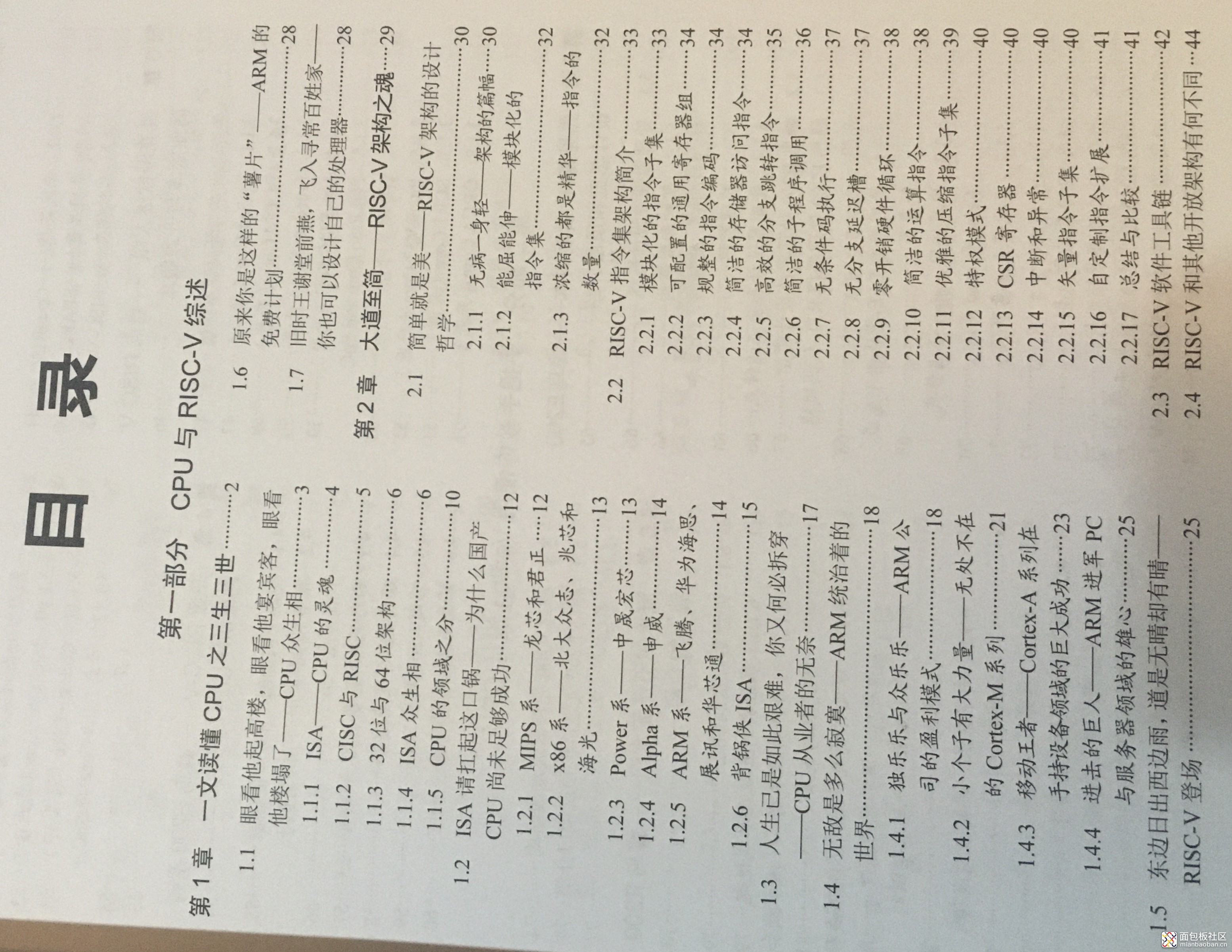

技术水平有保证了,语言水平如何呢?可以说,作者的语言除了清晰准确之外,还很生动活泼,这一点从本书的目录就可以看出,几乎每个章节的标题都既准确又生动,其中既有古典诗词也有网络流行语,看得出作者应该是一个阅读涉猎广泛的人。放一张图片大家感受下:

本书的章节划分清晰合理,每一章的篇幅都不太长,因此读来丝毫不觉得累。尤其是剖析源代码之前的那几个章节,对于有一定技术水平或视野的人来说,简直是读课外兴趣读物的感觉,非常畅快。因此我推荐每个对本领域感兴趣的读者都读一读这本书。

下面说一下阅读过程中印象最深的几个点吧:

- 1.1.1节中阐明了指令集架构和处理器微架构的概念和区别。之前对微架构的概念只是在网上看到,具体不甚了解。这个概念应该牢牢记住。

- 1.1.3节指出:指令集架构的位数是指通用寄存器的宽度,而不是指令编码的长度!比如,64位架构并不是说指令编码是64位的。这是一个常见的误区。虽然本人也是IC设计从业者,也做过MCU芯片,但对这一概念还是没有搞清,惭愧。今后要牢记。

- 2.2节,RISC-V指令集架构简介,分小节介绍了RISC-V指令集架构的16个特点。这一节非常重要,值得对RISC-V感兴趣的读者认真研读。其中,模块化的指令集是RISC-V指令集架构的一个非常鲜明的特点,似乎是其它各个指令集都不具备的,个人认为这是一个天才的构想。不过读完这一节,本人也有两个小小的疑问。(1)在这一节的多个子小节中都提到,RISC-V架构力图简化基本的指令集,从而简化硬件设计。那么,RISC-V架构是如何适用于高性能计算的?因为按照常规理解,简单的设计似乎应该适用于中低端应用,比如嵌入式、物联网等场合。书中提到,因为现代的高性能处理器的分支预测算法精度已经非常高,可以有强大的分支预测电路保证CPU能够准确地预测跳转执行达到高性能。但对于这一点目前本人的了解还很有限,只能留着以后学习了。(2)这一节中的“无分支延迟槽”和“零开销硬件循环”两个子小节的内容似乎不属于指令集架构的范畴,而是属于处理器微架构,即硬件实现方面的内容?为何RISC-V指令集架构中对这些也作出了规定呢?这个疑问恐怕也只能等对RISC-V有了更深入的研究后才能解开了。

- 5.3节,蜂鸟E200处理器核RTL代码风格介绍,其中的5.3.2节讲到,推荐使用assign语法替代if-else和case语法,并且给出了明确的理由,即:if-else和case不能传播不定态,且会产生优先级的选择电路而非并行选择电路,从而不利于时序和面积。这里讲的非常有道理,本人虽然从事RTL设计多年,但并没有注意到这一点,看来今后要把这一点作为代码风格规范应用到工作中。而对于5.3.1节所说的推荐使用标准DFF模块例化生成寄存器,本人倒是持一定的保留态度。

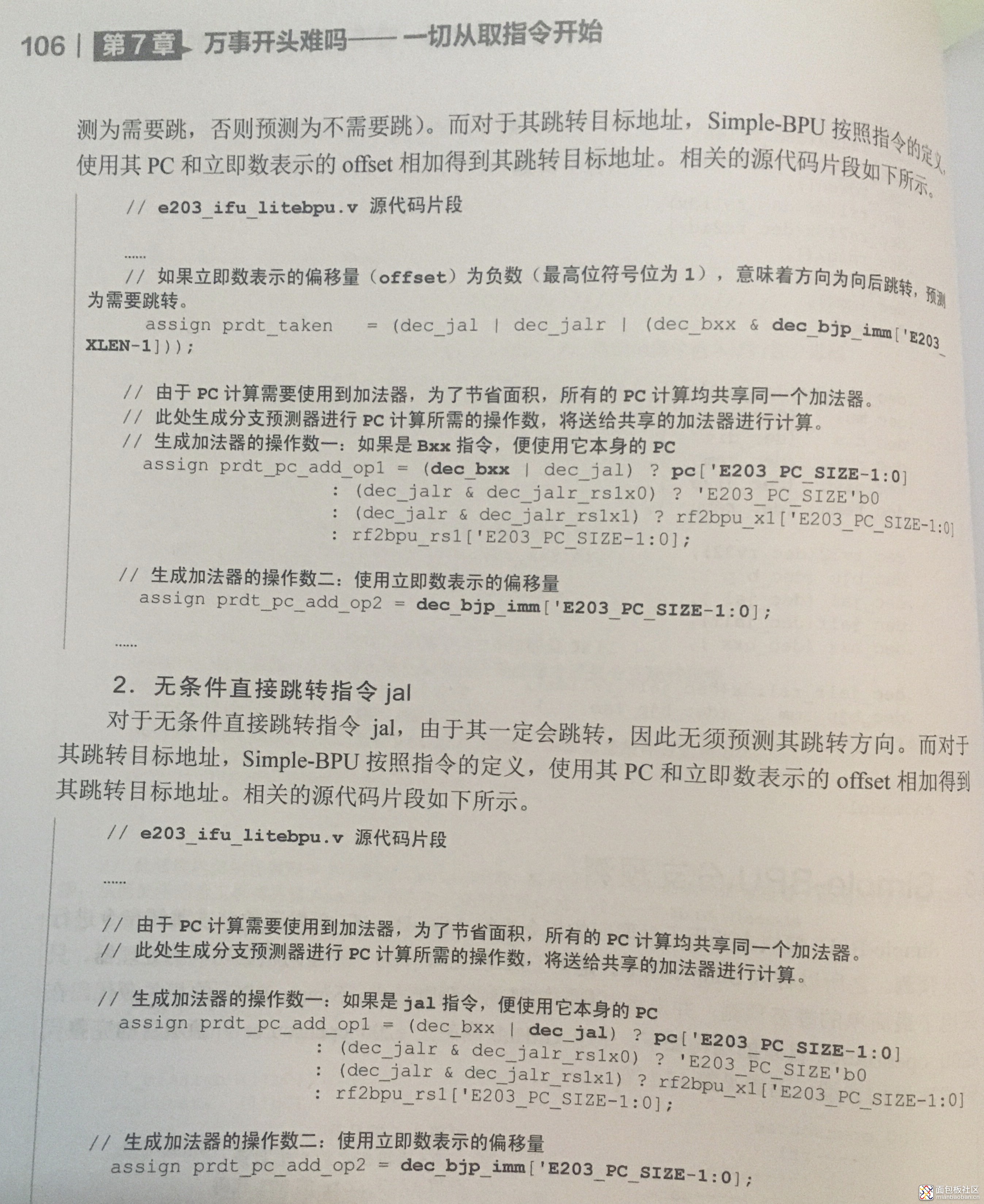

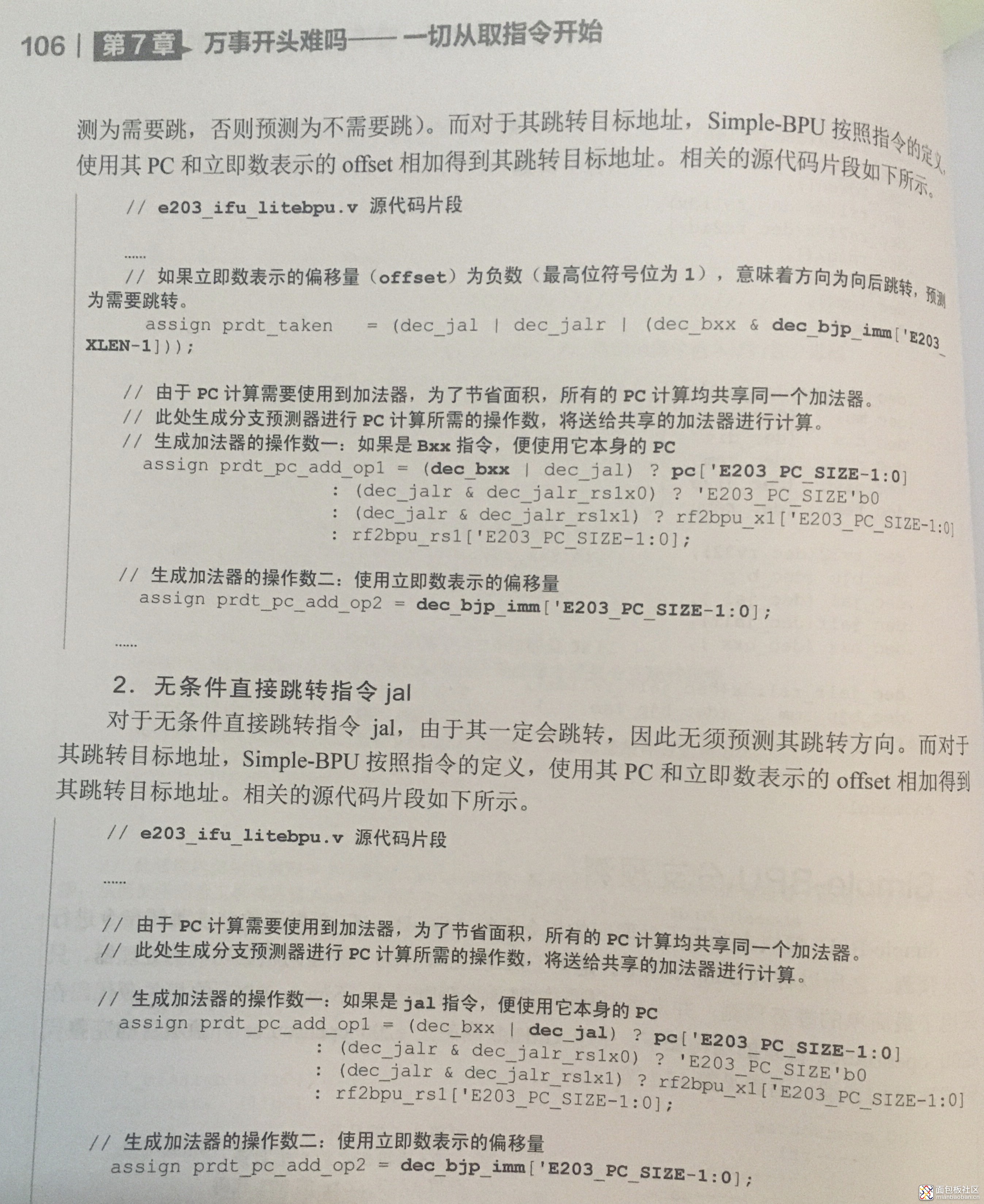

- 本书的代码示例部分很有特点,比如,同样一段代码,其中的不同分支对应书中不同小节的内容,在不同小节中就用加粗字体表示代码中的对应分支,便于读者的理解消化。可以看下图:

虽说这只是一个细节,但却能够反映出作者的用心之处。当然,我觉得光看书中的代码示例,应该是没法完全弄懂E203核的代码的,因为书中只是提取了重点内容对应的代码。详细源码还是要访问GitHub阅读。

由于时间有限,本人目前只阅读了七章,但感觉收获不小。相信通读全书后一定会处理器设计这一领域有较为全面的理解。

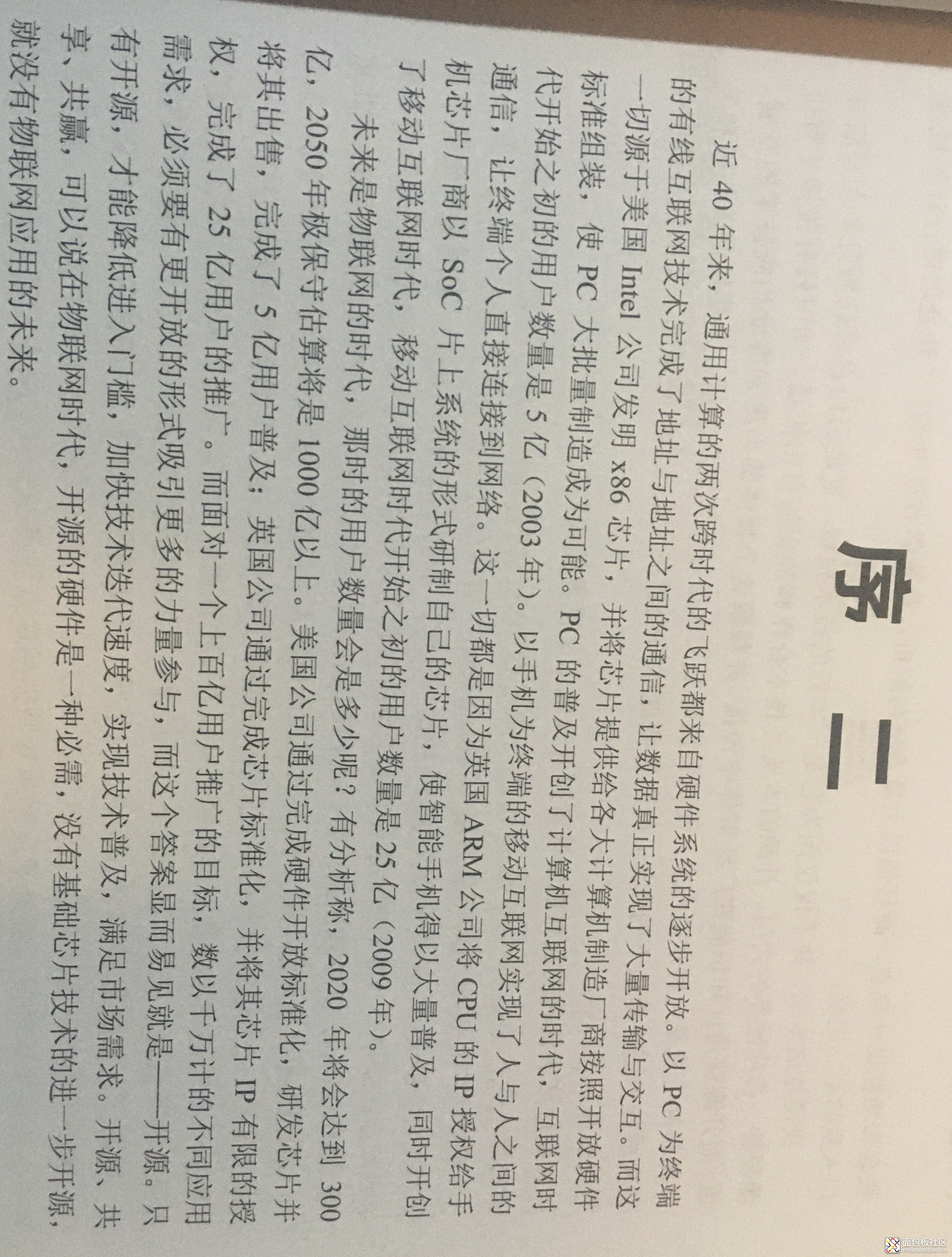

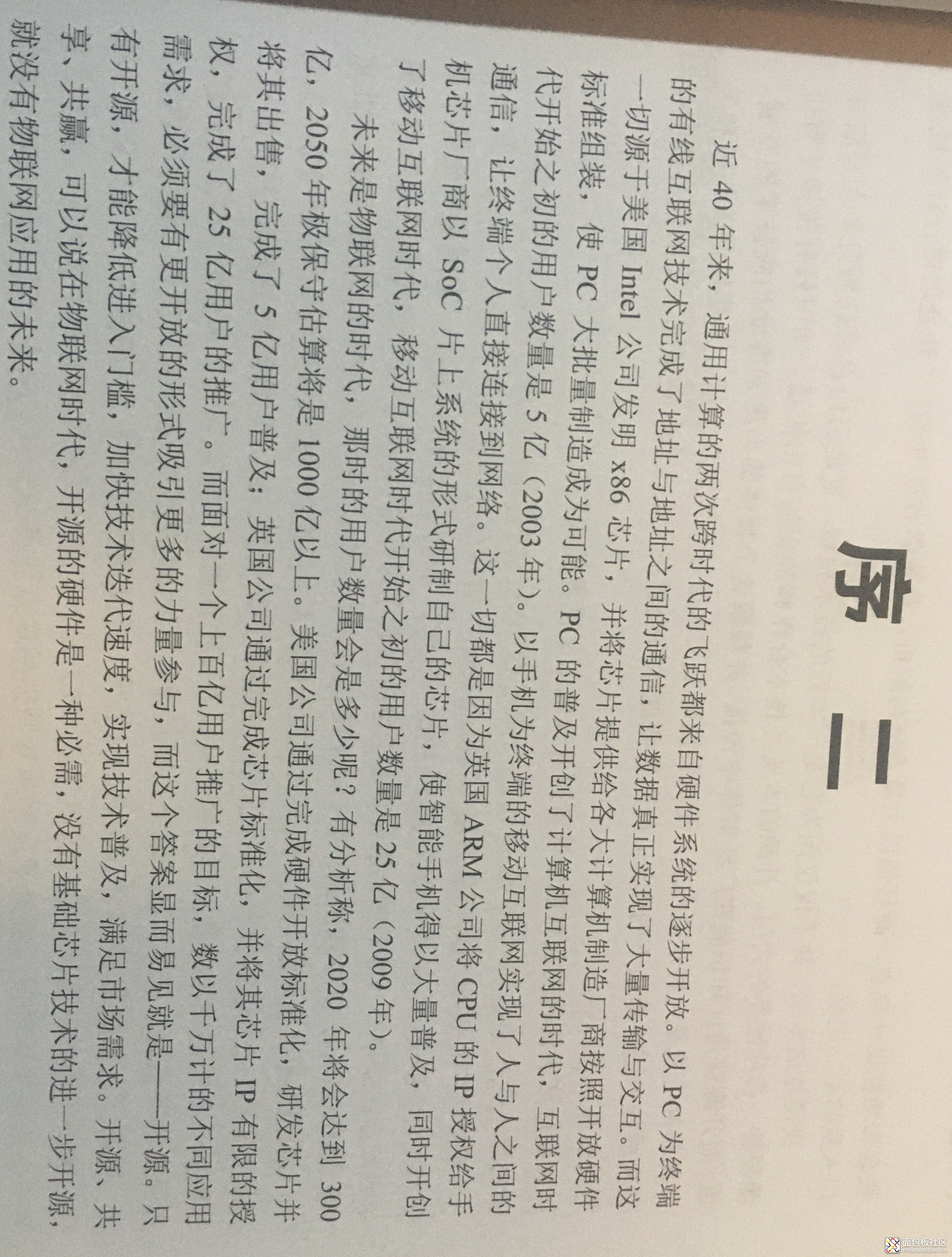

文章的最后,我想以本书序二中的一段话作为结束,见下图:)

这段话以高瞻远瞩的视角阐明了开源硬件兴起的必然性,我非常喜欢。而RISC-V很可能就是开源时代最耀眼的明星。时代的浪潮滚滚向前,你,跟上了吗?

作者: qdoverture, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1705123.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

curton 2019-11-4 19:26