ISP(In System Programmable)的使用越来越普及,无论是产品的生产、存储、维护还是版本控制,都很方便。

与非ISP(例如并行编程)相比,ISP的显著特点是占用的编程资源较少。正因为如此,我们可以将Microchip的ICSP、AVR的Serial Programming、Samsung的MTP、以及JTAG接口等理解为ISP。

以MCU为例,Data_sheet中都会给出ISP接口的实例。

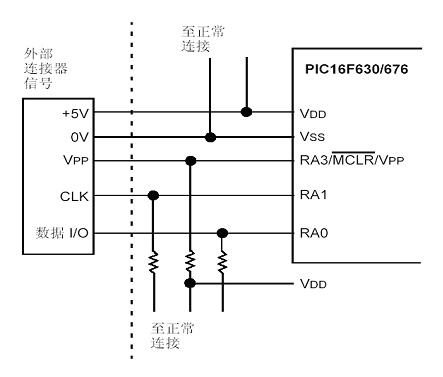

Microchip ICSP

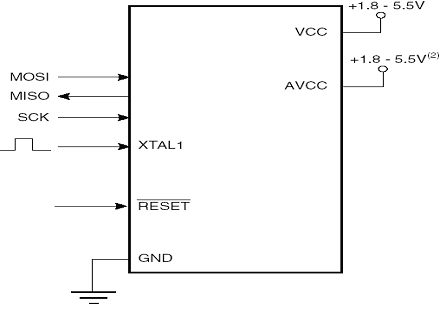

AVR Serial Programming and Verify

当然,与ISP相关的资源专用于ISP,是易于设计的。从系统成本出发,设计ISP与系统资源分时共用,将更具有挑战性。

每个厂家以及不同的器件对于ISP资源的定义是不同的,更多的情形是ISP与系统资源共用,在产品设计时有不同的考虑,但一个原则是:在ISP模式时,系统端相对于ISP_input和ISP_output为高阻,使ISP端口的电流被限制在3mA内为益。面对不同的系统端进行分类如下:

一.System_数字量输入

1K-10K电阻的加入,有效地隔离输入级对ISP信号的影响。

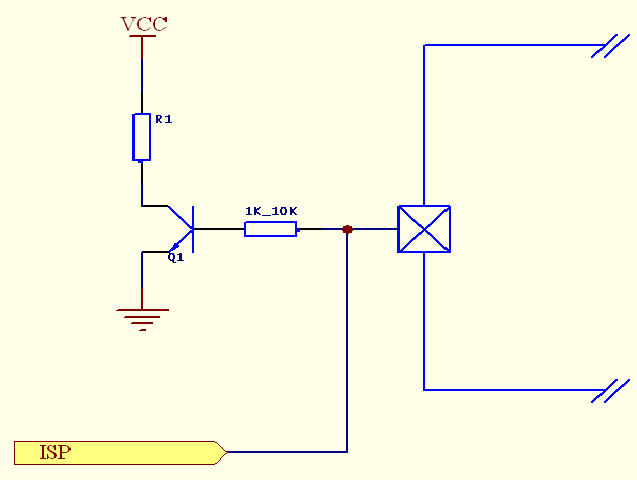

二.System_数字量输出

1k – 10k的选择应结合系统要求来设计,总的说来,系统的驱动能力与ISP编程器的驱动能力是相当的。

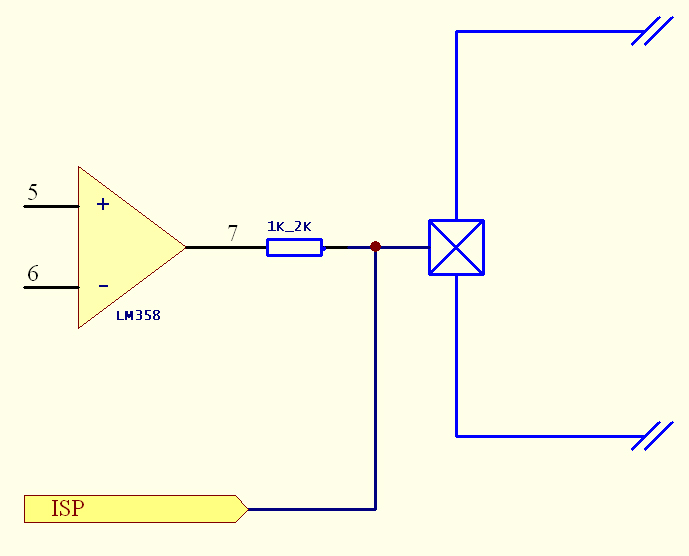

三.System_模拟量输入

相对于System_数字量输入,System_模拟量输入要考虑输入的等效内阻,小的滤波电容有时是必要的,特别是在要求高速ADC或比较器时。

四.System_模拟量输出

与System_数字量输出类似。

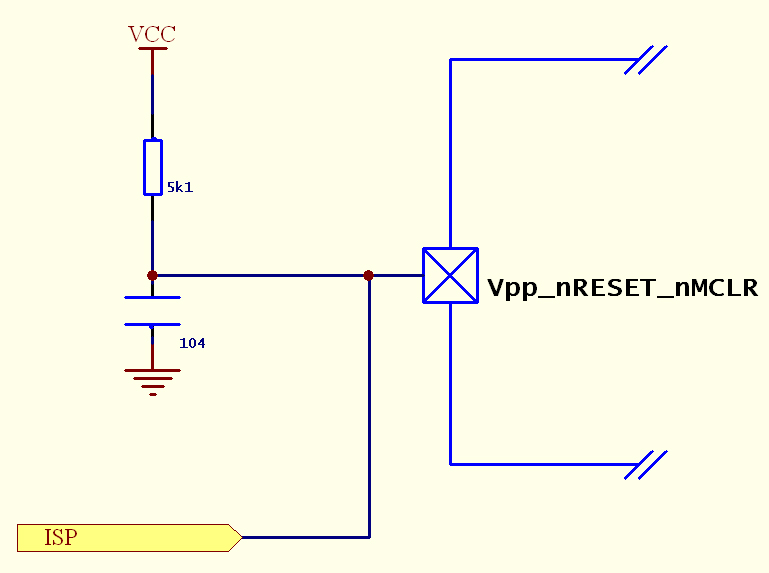

五.SPI模式选择_input

<?xml:namespace prefix = v />

很多MCU的SPI模式选择需要使用高压Vpp,此时Vpp端是没有上拉箝位二极管的,电容104需要选用25V或以上的耐压

/1

/1

文章评论(0条评论)

登录后参与讨论