//偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。如进行N倍偶数分频,那么可以通过由待分频的

//时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循

//环下去。这种方法可以实现任意的偶数分频。

module odd_division(clk,rst,count,clk_odd);

input clk,rst;

output clk_odd;

output[3:0] count;

reg clk_odd;

reg[3:0] count;

parameter N = 6;

always @ (posedge clk)

if(! rst)

begin

count <= 1'b0;

clk_odd <= 1'b0;

end

else

if ( count < N/2-1)

begin

count <= count + 1'b1;

end

else

begin

count <= 1'b0;

clk_odd <= ~clk_odd;

end

endmodule

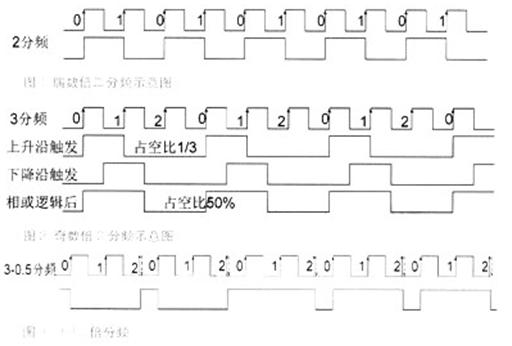

//奇数倍分频:归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数从零开始,到

//(N-1)/2进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。再者同时进行下降沿触发的

//模N计数,到和上升沿过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。两个占空比非50%的n分频时钟相或运

//算,得到占空比为50%的奇数n分频时钟。

module even_division(clk,rst,count1,count2,clk_even);

input clk,rst;

output[3:0] count1,count2;

output clk_even;

reg[3:0] count1,count2;

reg clkA,clkB;

wire clk_even;

parameter N = 5;

assign clk_re = ~clk;

assign clk_even = clkA | clkB;

always @(posedge clk)

if(! rst)

begin

count1 <= 1'b0;

clkA <= 1'b0;

end

else

if(count1 < (N - 1))

begin

count1 <= count1 + 1'b1;

if(count1 == (N - 1)/2)

begin

clkA <= ~clkA;

end

end

else

begin

clkA <= ~clkA;

count1 <= 1'b0;

end

always @ (posedge clk_re)

if(! rst)

begin

count2 <= 1'b0;

clkB <= 1'b0;

end

else

if(count2 < (N - 1))

begin

count2 <= count2 + 1'b1;

if(count2 == (N - 1)/2)

begin

clkB <= ~clkB;

end

end

else

begin

clkB <= ~clkB;

count2 <= 1'b0;

end

endmodule

网上看到的,很有帮助,zz与此

现来说说分频原理吧,原理通了,什么都好办了。

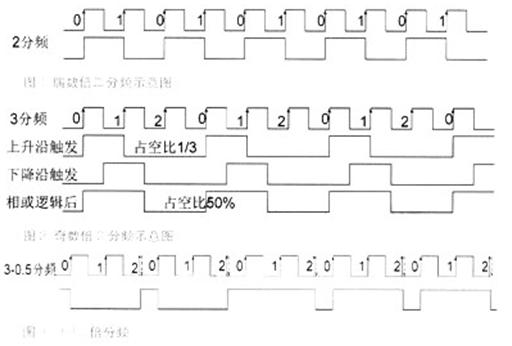

1. 偶数倍(2N)分频

使用一模N计数器模块即可实现,即每当模N计数器上升沿从0开始计数至N时,输出时钟进行翻转,同时给计数器一复位信号使之从0开始重新计数,以此循环即可。偶数倍分频原理示意图见图1。

2. 奇数倍(2N+1)分频

(1)占空比为X/(2N+1)或(2N+1-X)/(2N+1)分频,用模(2N+1)计数器模块可以实现。取0至2N之间一数值X(0,当计数器时钟上升沿从0开始计数到X值时输出时钟翻转一次,在计数器继续计数达到2N+1时,输出时钟再次翻转并对计数器置一复位信号,使之从0开始重新计数,即可实现。

(2)占空比为50%的分频,设计思想如下:基于(1)中占空比为非50%的输出时钟在输入时钟的上升沿触发翻转;若在同一个输入时钟周期内,此计数器的两次输出时钟翻转分别在与(1)中对应的下降沿触发翻转,输出的时钟与(1)中输出的时钟进行逻辑或,即可得到占空比为50%的奇数倍分频时钟。当然其输出端再与偶数倍分频器串接则可以实现偶数倍分频。奇数倍分频原理示意图见图2。(这也是许多公司常出的面试题,^_^,是不是很简单?)

3. N-0.5倍分频

采用模N计数器可以实现。具体如下:计数器从0开始上升沿计数,计数达到N-1上升沿时,输出时钟需翻转,由于分频值为N-0.5,所以在时钟翻转后经历0.5个周期时,计数器输出时钟必须进行再次翻转,即当CLK为下降沿时计数器的输入端应为上升沿脉冲,使计数器计数达到N而复位为0重新开始计数同时输出时钟翻转。这个过程所要做的就是对CLK进行适当的变换,使之送给计数器的触发时钟每经历N-0.5个周期就翻转一次。N-0.5倍:取N=3,分频原理示意图见图3。

<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

对于任意的N+A/B倍分频(N、A、B∈Z,A≦B)

分别设计一个分频值为N和分频值N+1的整数分频器,采用脉冲计数来控制单位时间内两个分频器出现的次数,从而获得所需要的小数分频值。可以采取如下方法来计算个子出现的频率:

设N出现的频率为a,则N×a+(N+1)×(B-a)=N×B+A 求解a=B-A; 所以N+1出现的频率为A.例如实现7+2/5分频,取a为3,即7×3+8×2就可以实现。但是由于这种小数分频输出的时钟脉冲抖动很大,现实中很少使用。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

/1

/1

文章评论(0条评论)

登录后参与讨论