部分转自

http://hi.baidu.com/rwen2012/blog/item/3eaf1b607236c9d88cb10d20.html

这两天做课程设计,发现有很多基础性的东西不大了解,呵呵,所以慢慢探索哈。

有一个是所谓的高阻态的问题...其实原来不太理解的原因是对硬件的东西不太了解。个人的理解是:(按51的P0口来讨论)在推挽输出的时候,上面的FET导通,输出为高电平;下面FET导通,输出为低电平;那么当两个FET都截止的时候呢?对地的电阻相当于无穷大(或者是不是可以理解为,此时输出的电平为VCC的一半,但是对地的电阻却是无穷大?),这大概就是所谓的高阻态。

所谓的数字电路的输出,大概也和这个一样。所以,所谓的“三态”应该只是针对输出而言

此时,输出端就相当于浮空(没有电流流动),其电平随外部电平高低而定,即该门电路放弃对输出端电路的控制,所以高阻态可以表征外部电平的真实值,所以A/D输入的时候用这个状态。

另外就是总线上面,许多个设备都是三态输出的,然后对于CPU来说,选中哪个器件,让其输出;对没有选中的器件,高阻态输出,这样就可以保证读到正确的值。

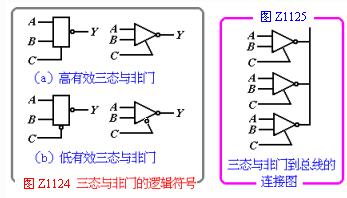

如上面图中Z1125所示,三态门共同挂接在数据总线上,所有的C(高阻态选择端)接CPU的控制信号。所以,同时只能有一路输出。当然,如果CPU的端口是OC/OD门,那么也可以实现线与。(我猜,比如PO口不接上拉电阻而用作IO方式)。

另外需要注意的几点:

一、高阻态既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,和没接一样,如果用万用表测的话有可能是高电平也有可能是低电平,随它后面接的东西定 。比如高阻态的输出和高电平相与,那么就和高阻态悬空是一个效果

二、好多单片机的输入是“高阻输入”,大概就是输入阻抗很高,比如A/D输入的口,肯定是输入电阻很大的,只是不知道叫“高阻态”正确否...

/5

/5

文章评论(0条评论)

登录后参与讨论