代码总述:

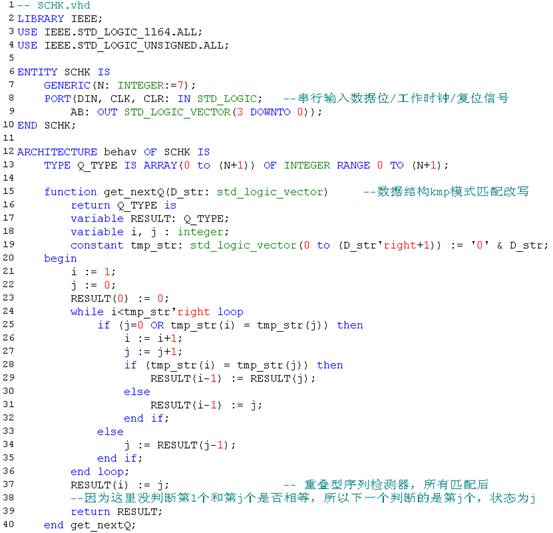

代码一:借鉴了数据结构模式匹配的KMP算法,并根据01序列检测器的特点进行修改,求出Q_next(当当前码不匹配时该转到的下一个状态),使得代码变得简单易懂,虽然KMP涉及的算法较为难懂,当程序的通用性是不言而喻的,只需要改变序列的长度,和序列,就可以检测不同的序列,而且时间复杂度为O(n+m)。

代码二:用符号化后,虽然看起来结构清晰了些,但反而少了很多优点。

代码三:看起来也是挺容易懂的,不过时间复杂度高了很多达到O(n*m)了。

符号化Moore型有限状态机代码如下:

https://static.assets-stash.eet-china.com/album/old-resources/2009/11/15/9e314189-66dc-4d59-bd2a-e985b28397be.rar

用移位寄存器的方法实现

https://static.assets-stash.eet-china.com/album/old-resources/2009/11/15/5af4cc68-d7b1-4149-a158-683da2c97516.rar

实验报告:

/5

/5

文章评论(0条评论)

登录后参与讨论