接上文

其中Qij,Xij,Cij和Dij分别是4*4数组Q,X,C,D中元素。Cij和Dij可以表示如下:

其中,

Wij是输入矩阵W中的元素。因而,4*4反向变换的SFG可以表示为图2。

A. 给出的可重构2-D 结构

SFG可以合并在一个可重构2-D结构中,此结构可以支持所有的三个变换。所有的结构如图3表示。

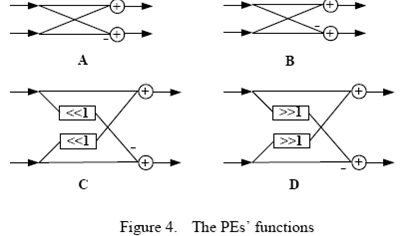

它包含32个处理器单元(PE)和4个可重构内部连接器。有3种Pes结构,功能如图4表示。

PE1功能是不变的,而PE2和PE3的功能是可重构的。PE1功能如图4—A中所示。对于4*4前向DCT而言,PE2和PE3可以配置成按图4**能C和功能A工作。对于反向DCT,PE2和PE3可以配置成按图4**能A和功能D工作。对于Hadamard变换,PE2和PE3可以配置成按图4功能B和功能A工作。内部连接器P_IN,P_C1,P_Tran和P_C2可以独立的配置为如下功能:M1X(或M1W),M2A(或M3C),M1PT(或M3QT)和M2B(或M3D)。

所有可重构内部接口可以用数据选择器实现。移位器可以用硬线实现,不会引入延时和面积。4*4数据块可以用并行方式载入。4*4变换的结果可以在一个周期内输出。

四:实现和结果对比

所给出的多变换可重构结构采用Verilog_HDL描述。仿真采用Cadence下NC_Verilog和Synopsys DC,所用工艺为TSMC 0.18um CMOS标准单元库。设计处理速度为16 pixels/cycle。即一个周期内可以计算出4*4变换。电路可以在200MHz工作,且处理速度为3.2G pixels每秒。在频率为100Mhz,可重构结构可以实现以60fps速度实时处理4096*2048。

图1给出了典型设计和本设计的主要特点,包含CMOS技术,硬件消耗(以门级为计量单位),最大工作频率,数据处理速率(DPR,pixels/cycle),吞吐量(TP,pixels/second)和每单位面积的数据吞吐率(DTUA)。DTUA通常是评估硬件效率的,数据吞吐率比上硬件消耗。DTUA越高,结构效率越高。根据表1中DTUA的情况,本设计的效率较其它设计更好。

五:总结

本文提出了一种针对H.264中4*4变换的高性能可重构2-DCT变换结构。给出的直接2-D变换SFG没有使用转置存储器。所介绍的结构可以提高数据的处理速率为16pixels/cycle。使用TSMC 0.18um标准单元库,多变换的电路的最优频率为200mhz实现3.2Gpixels/s,面积消耗未11038个gates。就DTUA而言,相比已经存在的结构,本设计具有更好的性能。

/1

/1

文章评论(0条评论)

登录后参与讨论