本文参考Xilinx PCIE应用用户手册,如有疑问可以参考源手册《xapp1052》

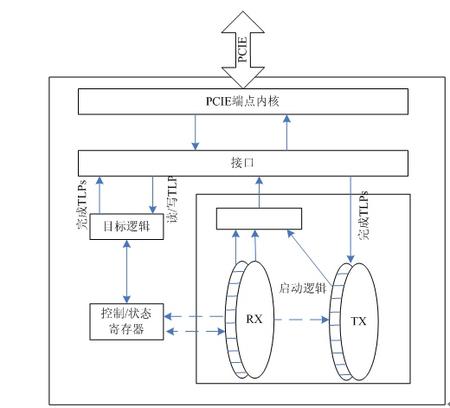

BMD结构如图所示。BMD由五部分组成:启动程序逻辑、目标逻辑、状态/控制寄存器、接口逻辑和PCIE 端点内核。

图 BMD结构图

目标逻辑

目标逻辑的作用是负责捕获接口上的单双字节内存写(MWr)和内存读(MRd)TLPs。内存写和内存读通过可编程输入输出被发送到终端上,进而监控DMA硬件。目标逻辑的功能是在内存写和反馈内存读完成时更新状态和控制寄存器的值,所有内存写数据包是32bit,包含一个双字节负载。传入的内存读数据包只响应一个双字节的数据,同时由于完成一个双字节数据。

控制状态寄存器

控制状态寄存器包含DMA控制器的操作信息。提供的示例BMD的设计用来测量数据传输的性能。因此,状态寄存器不是必须要的,用户可以根据需求进行删除。所有寄存器的定义在“附录A:设计描述寄存器”。

启动逻辑

该部分的功能是根据上传还是下载传输被选中相应的产生内存写或读TLPs。总线主设计在同时刻只支持产生一种类型的数据流。总线主设备使能位(PCI命令寄存器的Bit2)必须设置为启动TLPs传输流。传输容量最大为4k。

当从终端向系统内存传输数据时,启动逻辑产生内存写TLPs。DMA写控制和状态寄存器必须指定地址、位宽、有效内容以及TLP的个数。

第一个TLP包括启动地址,该地址由写DMA TLP的地址(详情参考“Write DMA TLP Address(008H,R/W)”,附录A)寄存器给出。其后的TLPs包括一个地址由存在寄存器WDMATLPA的值加上存在写DMA TLP大小寄存器的值(Write DMA TLP Size(WDMATLPS)(00CH, 附录A))。在内存写的时候,启动逻辑指定了数据模式。每个双字节包括了写DMA 数据模式寄存器的内容(Write DMA Data Pattern(WDMATLPP)(014H))。注意,在正常情况下,数据应包括被移动到主机内存的设备信息。然而,例如参考的设计,它是一个固定模式在WDMATLPP寄存器里。

当MWr TLPs个数与内部的Write DMA TLP Count的值相同时会产生一个中断。表3是一个DMA写操作的事件顺序。

表3 DMA写操作事件顺序

|

步骤 |

操作 |

寄存器操作 |

真值 |

|

1 |

启动逻辑复位 |

PIO写DCR1 |

0x00000001 |

|

2 |

撤销复位 |

PIO写DCR1 |

0x00000000 |

|

3 |

写DMA H/W地址 |

PIO写WDMATLPA |

H/W 地址 |

|

4 |

写DMA TLP的大小 |

PIO写WDMATLPS |

写TLP的大小 |

|

5 |

写DMA TLP的数量 |

PIO写WDMATLPC |

写TLP的数量 |

|

6 |

TLP的负载模式 |

PIO写WDMATLPP |

数据模式 |

|

7 |

开始DMA写 |

PIO写DCR2 |

0x00000001 |

|

8 |

等待TLP中断 |

||

|

9 |

写DMA性能 |

PIO读WDMAPERF |

当系统内存向终端传输数据时,启动逻辑产生内存读TLPs。读DMA给出地址、数据大小、有效负载内容、发送TLP的个数。

第一个TLP的地址由读DMA TLP的地址(RDMATLPA寄存器)寄存器给出。其他的TLP在传输时的地址由RDMATLPA寄存器的值加上RDMATLPS寄存器的值给出。TLP的标签的值由0开始增加,保证每个数据包对应一个编号。在完成数据传输后收到内存读请求包的响应。启动逻辑跟踪数据的收入完成,并且计算接收数据的总数。当接收到已请求的数据包,终端会产生一个中断,上传提示DMA传输结束。此外,在启动逻辑里也执行错误检错。每一个双字节在完成负载的值必须与RDMATLPP寄存器的值匹配。有效负载总数与RDMATLPC的值乘以RDMATLPS。图4是一个DMA读操作的事件顺序。

表4 DMA读操作事件顺序

|

步骤 |

操作 |

寄存器操作 |

真值 |

|

1 |

启动逻辑复位 |

PIO写DCR1 |

0x00000001 |

|

2 |

撤销复位 |

PIO写DCR1 |

0x00000000 |

|

3 |

读DMA H/W地址 |

PIO写RDMATLPA |

H/W 地址 |

|

4 |

读DMA TLP的大小 |

PIO写RDMATLPS |

读TLP的大小 |

|

5 |

读DMA TLP的数量 |

PIO写RDMATLPC |

读TLP的数量 |

|

6 |

开始DMA读 |

PIO写DCR2 |

0x00010000 |

|

7 |

等待TLP中断 |

||

|

8 |

读DMA性能 |

PIO读WDMAPERF |

通过PCI指令寄存器中断屏蔽位或者MSI使能位是TLP中断的两种类型。当MSI使能位被置1时,终端内核将通过发送一个MWr TLP产生一个MSI请求;当MSI使能位清零时,终端将产生一个中断在PCI 指令寄存器的第10位启动中断时。

当应用程序只关心数据的传输过程时,从内存读请求的返回数据将被BMD遗弃。正常情况下,这数据应该按正确的顺序去检查,存储到RAM或FIFO里面。 /1

/1

文章评论(0条评论)

登录后参与讨论