一:组合逻辑环

1)

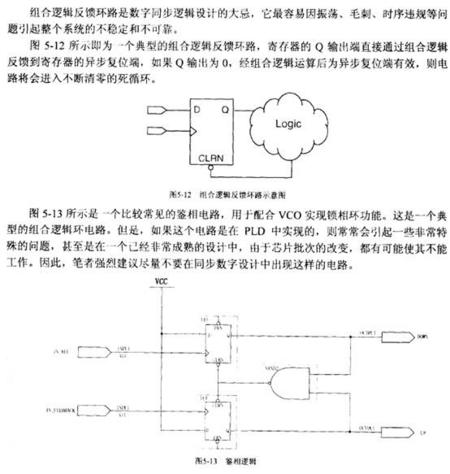

组合逻辑反馈环路是数字同步逻辑设计的大忌,它最容易因振荡、毛刺、时序违规等问

题引起整个系统的不稳定和不可靠。

组合逻辑反馈环路是二种高风险的设计方式,主要原因如下:

1.组合反馈环的逻辑功能完全依赖于其反馈环路上组合逻辑的门延时和布线延时等,如果

这些传播延时有任何改变,则该组合反馈环单元的整体逻辑功能将彻底改变,而且改变后

的逻辑功能很难确定。

2.组合反馈环的时序分析是无穷循环的时序计算,综合、实现等EDA 工具迫不得已一般必

须主动割断其时序路径,以完成相关的时序计算。而不同的EDA工具对组合反馈环的处理

方法各不相同,所以组合反馈环的最终实现结果有很多不确定因素。

3.通常的综合工具(synplify_pro)在处理组合逻辑反馈问题时,将产生Latch,这将对时

序造成许多问题。

【例】 这是一个组合逻辑反馈的例子,o_mux根据输入条件i_sel进行选择,当

i_sel = 0, 选择i_a作为输出,当i_sel = 1,选择i_b作为输出,当i_sel为其他值时候,

设计试图通过组合逻辑反馈使输出能够保留原来的值,这个时候问题就出现了,由

于使用了组合逻辑的反馈,综合工具会将把o_mux当作锁存器(Latch)输出,而不

会产生反馈逻辑。

// 这是一个组合逻辑反馈的例子,设计中应当避免

module comb_fead_back

(

input [1:0] i_sel,

input i_a,

input i_b,

output reg o_mux

);

always @(i_sel or i_a or i_b) begin

if (i_sel == 2'b00) begin

o_mux = i_a;

end

else if (i_sel == 2'b01) begin

o_mux = i_b;

end

else begin

o_mux = o_mux;

end

end

endmodule

2)

3)

2)

无意识锁存器产生的主要原因有两个:一是在设计组合逻辑中使用不完整的条件判断

语句,即有if没有else,而是在设计组合逻辑中使用不完整的case语句;另外一个是设

计中使用到了组合逻辑反馈等异步逻辑。

/5

/5

文章评论(0条评论)

登录后参与讨论