今天熊猫君要分享的是如何使用Xilinx ZYNQ Ultrascale+ MPSoC的PS端原生DP接口实现LIVE模式输出3860*2160,30Hz视频。

熊猫君先介绍下开发环境:

a)板子:自制MPSoC电路,基于ZU4EV;

b)硬件开发环境:Vivado2021.1;

c)软件开发环境:Vitis 2021.1,运行裸机测试程序。

(一)介绍一下PS端的DP接口:

(1)支持2-LANE 5.4Gbps,符合VESA DisplayPort v1.2a规范;

(2)支持4K 30Hz视频输出,支持仅Y,YCbCr444,YCbCr422,YCbCr420,RGB等各种格式,支持6、8、10、12bit色彩深度,支持48KHz音频输出;

(3)支持视频接口和图形接口叠加,支持上采样和将采样;

(4)支持DPDMA直接从DDR Frame buffer读取视频源或来自PL的实时LIVE视频。

(二)为什么要使用Live模式?

一般的应用,都是直接通过DPDMA直接从DDR的Frame Buffer读取视频流和图形流进行显示。使用PL端直接输入的LIVE模式,主要是为了减少显示延时。PL端处理的结果如果先写入DDR再通过DP显示的话,要经过帧缓存管理,至少需要增加2帧以上的延迟,无法满足一些延时需求苛刻的场合,因此,这个时候LIVE模式就有它的优势了。

(三)Xilinx MPSoC PS端原生DP接口有哪些缺陷呢?

这个原生DP接口实际上是不太完整的,主要是因为它只能支持2-LANE 5.4Gbps,也就是说最高性能只能到4K 30Hz,无法满足许多场合最低要求4K 60Hz的硬性需求;由此,还派生出另外一个问题,如果是显示设备有DP接口还好,如果只有HDMI接口的话,就需要转接,这个DP转HDMI转接线的选取还极其的难,有讲究,否则就用不了,或握手训练不成功,或显示黑屏等:

a)必须是主动式的,意思是要有转接芯片,支持AUX握手(不能是IIC-OVER-AUX)进行通道和速率切换、训练的;

b)必须是支持最少4K 60Hz的主动式转接线,输出接口至少是可以支持HDMI2.0的。

(四)ZYNQ Ultrascale+ MPSoC IP核的配置

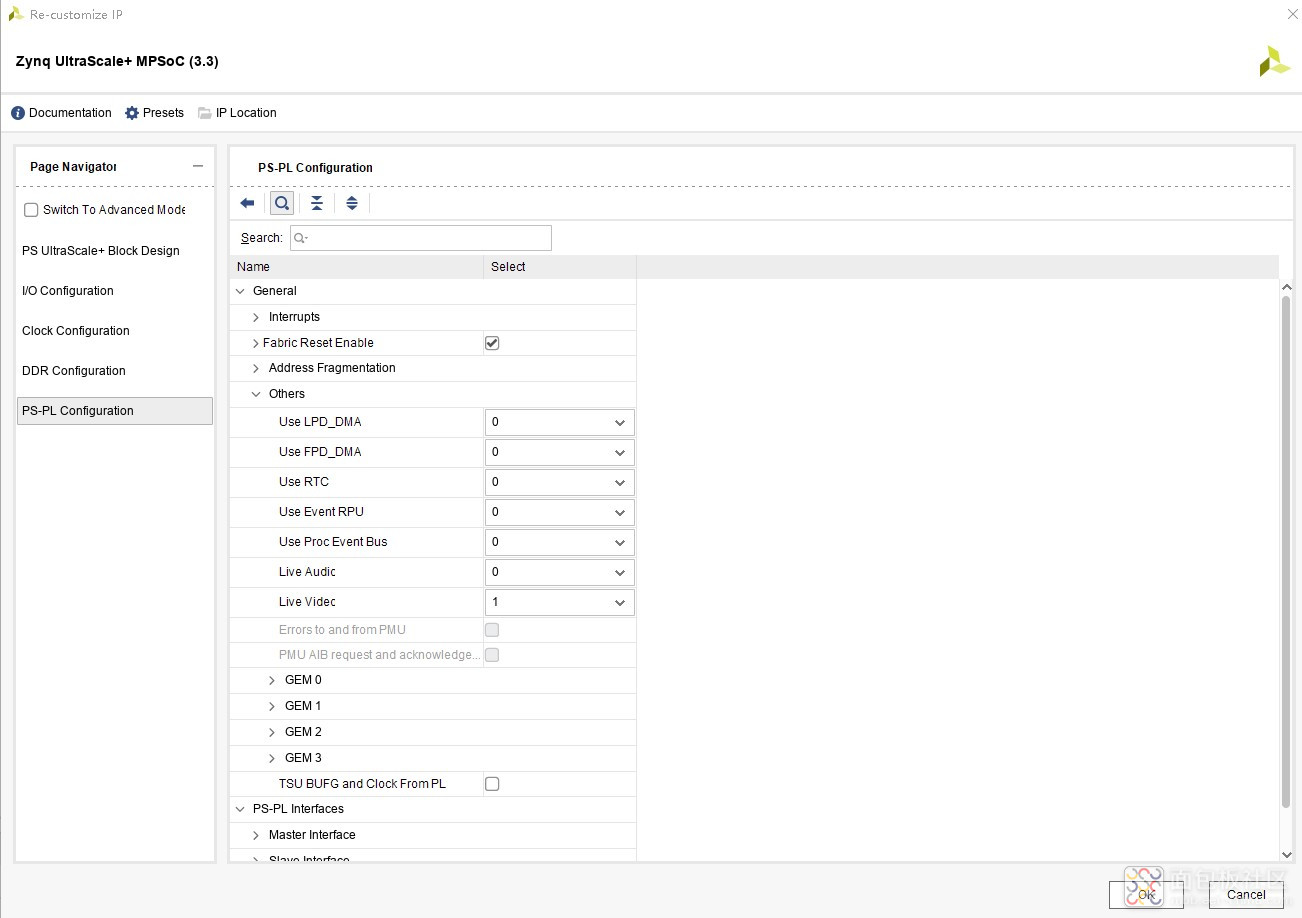

IP核的配置如下,将Live Video置‘1’,如果需要音频,就将Live Video置‘1’,如下图:

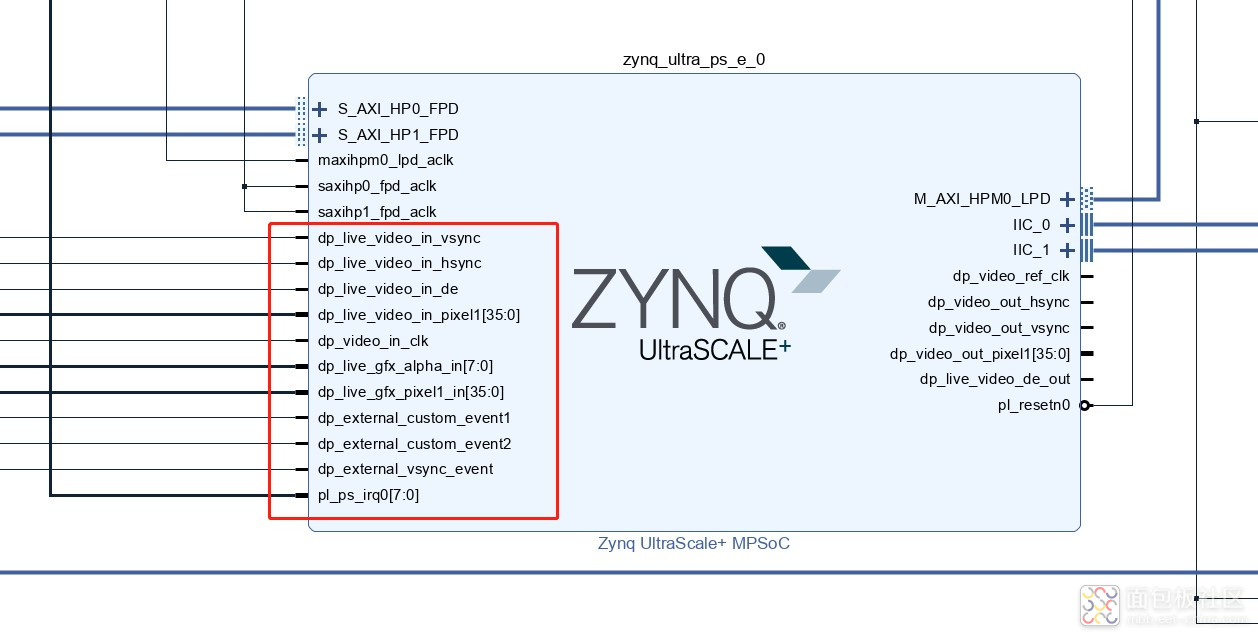

然后,IP就会新增DP LIVE引脚,标准的BT1120时序接口,如下图:

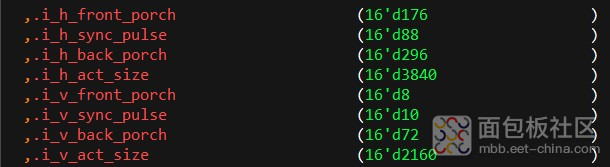

如果需要4K 30Hz显示,那么dp_video_in_clk就需要270MHz,详细的时序参数自行阅读标准文档CEA-861-G,如下图:

(五)Vitis端的测试程序

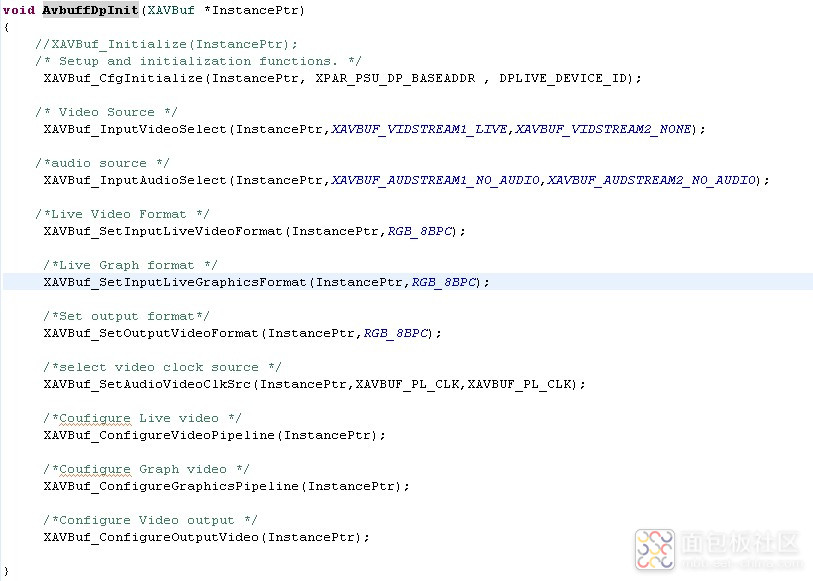

测试程序其实简单很多,只需要将avbuff驱动里面设置为live模式,然后Dp驱动里面做好aux握手和lane数、速率训练即可。无需通过中断做帧缓存管理,PL端输入的时序正确就行了。

(六)PL产生的测试彩条运行效果

顺便,熊猫君还想提一嘴,就是对各种电视的兼容性强、转换稳定的DP转HDMI线真的不好找,一些常见的厂家比如毕亚兹、也仁、胜为、山泽、晶华、威迅、绿联的都试过,最好使的还是绿联的一款支持4K/60Hz的主动式转接线,到目前为止,市场上主流的电视还没有出现兼容性不好或传输不稳定的情况。

作者: panda君, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3403128.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/1

/1

文章评论(0条评论)

登录后参与讨论