同步时序约束——Output Delay

<="FONT-SIZE: 12pt">Output Delay

首先,我们知道板级时钟偏斜(clock skew)=时钟源到达外部器件的时间—时钟源到达FPGA端口时间。

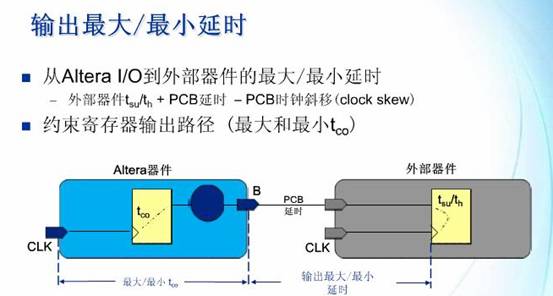

Altera官方课件见图1

图1 输出最大/最小延时

们可以约束的,其它的参数都是板级参数,无法用FPGA控制。还有一点就是这次的研究对象时外部器件,即对时钟到达外部器件时钟引脚的时间和数据到达外部器件D数据口的时间进行比较。

们可以约束的,其它的参数都是板级参数,无法用FPGA控制。还有一点就是这次的研究对象时外部器件,即对时钟到达外部器件时钟引脚的时间和数据到达外部器件D数据口的时间进行比较。

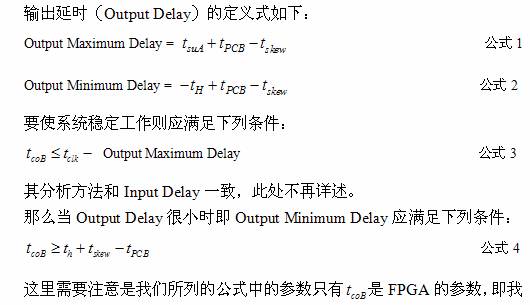

下面分析一下Output Maximum Delay和Output Minimum Delay

该部分内容参考了Altera应用笔记《Constraining and analyzing Source-Synchronous Interfaces》Page 11

首先,我们还是要明确一下,那就是所谓的Output Delay是指对于同一器件数据到达时间相对于时钟到达时间的差值。

1. Output Maximum Delay

何时会出现最大输出延时呢?当数据传输路径最长和时钟传输路径最短时,会使输出延时最大。

Output maximum delay value = maximum trace delay for data + ![]() of external register – minimum trace delay for clock 公式5

of external register – minimum trace delay for clock 公式5

公式5中,之所以会有![]() of external register是因为数据到达后经过一定的建立时间

of external register是因为数据到达后经过一定的建立时间![]() 后,时钟才会到达。

后,时钟才会到达。

2. Output Minimum Delay

Output minimum delay value = minimum trace delay for data - ![]() of external register – maximum trace delay for clock 公式6公式6中之所以会有

of external register – maximum trace delay for clock 公式6公式6中之所以会有![]() of external register是因为数据到达之前的

of external register是因为数据到达之前的![]() 时间,时钟已经到达。

时间,时钟已经到达。

/5

/5

文章评论(0条评论)

登录后参与讨论