作者:Paul Graykowski

半导体开发目前正处于由新技术和方法共同驱动的快速发展阶段。将多种功能组合到片上系统 (SoC) 中的技术正变得越来越复杂。数据中心、机器人技术、ADAS 和人工智能/机器学习 (AI/ML) 等细分市场新技术的快速发展催生了新型 SoC。这些领域要求设计能够最大限度提高功率效率和运行效率。设计人员发现,片上网络 (NoC) 提供了能够满足这一需求的支持技术,因此,正加速从交叉开关(crossbar)互连技术向NoC过渡。

许多设计团队正在从crossbar互连过渡到 NoC,以减少拥塞、简化时序收敛,并优化目标带宽和延迟。采用基于 NoC 的互连有助于设计人员更好地优化日益复杂的 SoC。但是,采用NoC互连以后是否还有进一步的优化机会呢?正如许多大型 SoC 的制造商所发现的那样,答案通常是肯定的。此外,NoC 技术还可以进一步优化 RTL 重新分区。

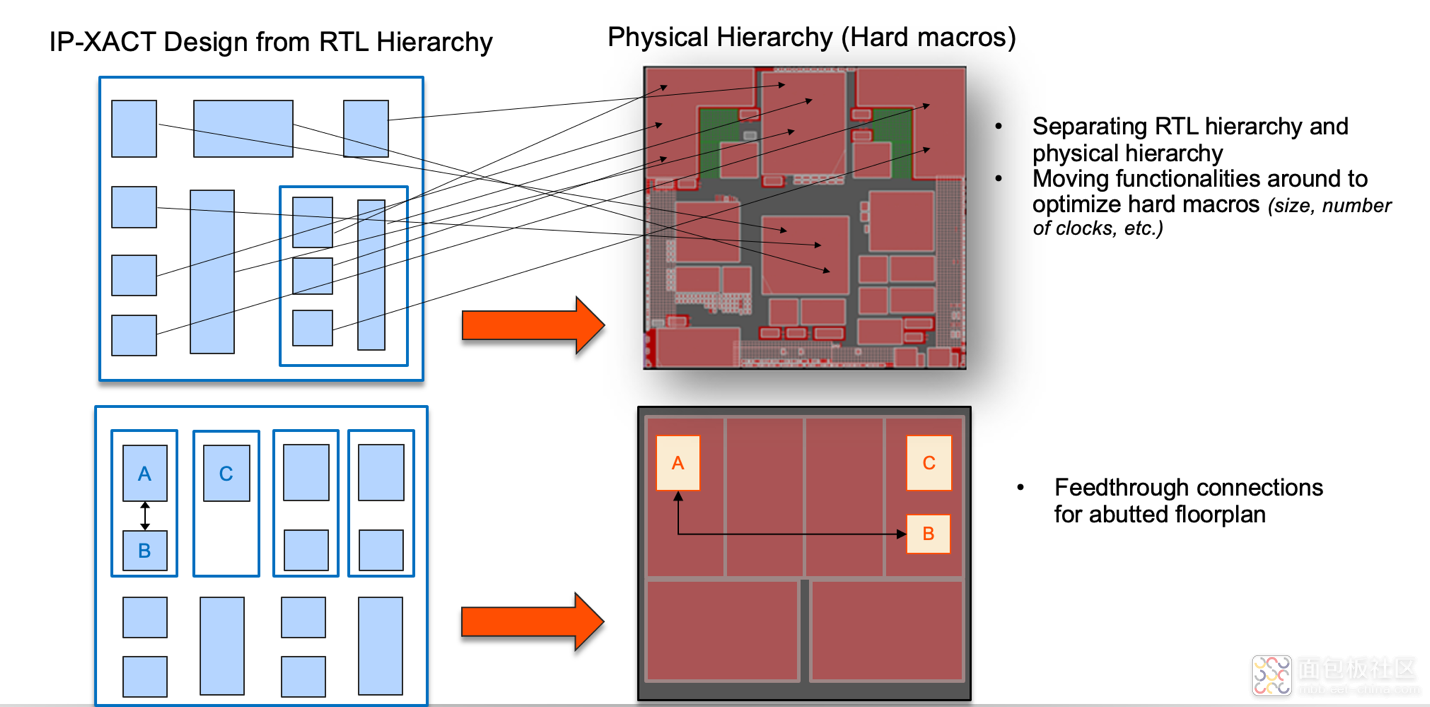

对物理设计进行 RTL 重组:最小化块间引线长度(上),通过邻接实现最大化连接(下)

进一步优化的机会?

采用crossbar设计时,其四周有许多连接布线和逻辑块,在紧凑的平面图中,可用于布线的通道非常狭窄,因此,这些布线和块不可避免地纠缠在一起。 随着这些连接变得更加复杂,往往迫使设计面积不断扩大。而NoC 类似于网络,其分支很容易穿过狭窄的空间,因此不需要特别将各块分开。

但是 NoC 只能优化到平面图中块之间的间隙允许的程度。 如果间隙不够大,则必须将这些块互相分开一些,以便为宽互连腾留出足够的空间(这样会增加设计面积),或者必须绕过一些中间块布线(这样会增加延迟)。如果能够减少这些限制,则可以实现进一步优化。

RTL重新分区

功能块成为互连布线的天然屏障,并受 RTL 层次结构的限制。他们在物理实现上的尺寸和纵横比各不相同 - 从大到小,从方形到细长。较大的块会产生更多的障碍,而过多的小块则会限制物理合成以优化逻辑的机会。寻找最佳的平面图解决方案需要反复试验,但项目进度可能会限制用于此的时间。设计人员需要灵活地调整块的边界,通过拆分或合并功能来找到更利于互连布局的解决方案。

物理设计工具可以做到这一点,但 RTL 层次结构的边界是限定的。为了进行分区试验,必须在 RTL 中进行手术式改变,这是可能的,但具有挑战性。需要考虑将一个块分割成两个,将一些块合并到一个新的层次结构中,或者将一个块从其父级层次结构中分离出来。这些在概念上都很容易描述,但实现起来却很复杂。

连线/总线必须在块内的 RTL 中和上一级结构重新拼接,必须创建或删除端口。必须谨慎对待现有的连接交叉点、引线和撤销更改。对于如何处理这些情况,通常有多种答案。实施团队在试验中尽其所能,但由于时间限制,只能进行少量试验。

避免互连线因绕过障碍物而增加延迟的另一种方法是让它通过块,允许相邻块通过邻接直接连接。物理设计工具可以支持添加简单的引线。 NoC 结构可以随着设计的发展而重新配置,但这可能在每次物理设计通过时需要重新启动。避免这种麻烦的一种方法是通过类似重新分区的功能在 RTL 中定义引线。

Arteris IP SoC/HSI 自动重新分区

采用自动化进行重新分区工作是显而易见的解决方案,而 Arteris IP 正好具有该功能,已在许多客户中得到验证。如果需要,该技术可以支持每天多次通过。设计团队仍然需要对每一代设计进行等效性检查。虽然如此,这种自动化方法比手动方法要容易得多。 这里 可以了解更多。

作者: ArterisIP, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-3893295.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/1

/1

文章评论(0条评论)

登录后参与讨论