前段时间,参加了一个比赛,题目大概就是用verilog设计HDB3 编码及其解码电路,一直犹豫没有写博文的原因就是其实我也没太弄懂,不好意思丢人。

但是后来想了想,还是觉得要记录一下,顺便说一下自己小小的学习心得,主要是HDB3的Verilog资料太少了!!!比赛之前我在网上找了半天都只能找到一点,所以也算是给后面学的人一点经验。

比赛虽然有一些其他的结构,比如用m序列产生随机数啥的,但是这些部分资料比较多,我就不说了,主要说一下用verilog设计HDB3 编码及其解码电路的思路吧。

1. HDB3码的原理

一开始看到这个题目一脸懵,主要是不知道HDB3是干什么的,实际上HDB3用文字描述很简单,下面一段是引用的([1]吴海涛,陈英俊,梁迎春.基于FPGA的HDB3编解码器设计[J].微计算机信息,2008(17):236-238.)

在消息的二进制代码序列中:

(1)当连“0”码的个数不大于3时,HDB3编码规律与AMI码相同,即“1”码变为“+1”、“-1”交替脉冲;

(2)当代码序列中出现4个连“0”码或超过4个连“0”码时,把连“0”段按4个“0”分节,即“0000”,并使第4个“0”码变为“1”码,用V脉冲表示。这样可以消除长连“0”现象。为了便于识别V脉冲,使V脉冲极性与前一个“1”脉冲极性相同。这样就破坏了AMI码极性交替的规律,所以V脉冲为破坏脉冲,把V脉冲和前3个连“0”称为破坏节“000V”;

(3)为了使脉冲序列仍不含直流分量,则必须使相邻的破坏点V脉冲极性交替;

(4)为了保证前面两条件成立,必须使相邻的破坏点之间有奇数个“1”码。如果原序列中破坏点之间的“1”码为偶数,则必须补为奇数,即将破坏节中的第一个“0”码变为“1”,用B脉冲表示。这时破坏节变为“B00V”形式。B脉冲极性与前一“1”脉冲极性相反,而B脉冲极性和V脉冲极性相同。

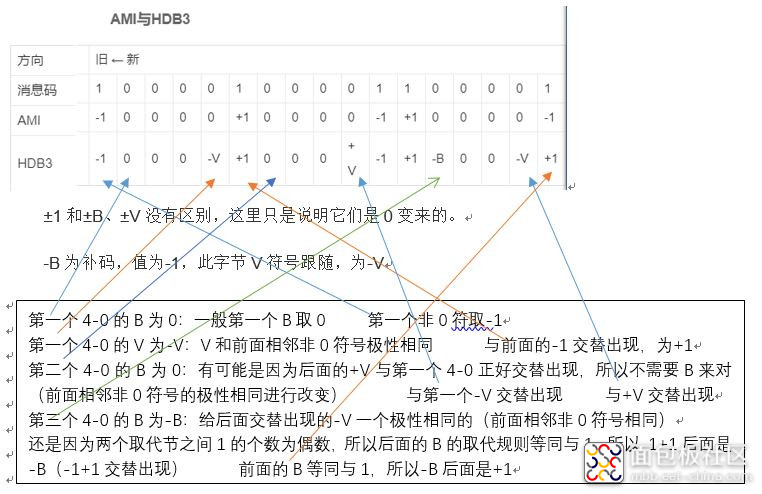

看着大家可能会觉得很晕,其实举一个例子大家就明白了(✌,我弄懂怎么上转照片了)

1、源码是1时,暂时不变;

2、连0不超过3个时不变,有4个或以上连0时把每4个0换为取代节,即B00V;

3、确定B是0还是±1:第一个B一般取0,若两个取代节之间1的个数为偶,易推得后者的B一定是±1,此时B和1遵循的规则完全相同,可以直接记为1,即100V;为奇则一定是0,记为0,即000V。

4、B和V具体值满足以下条件:V和前面相邻非0符号极性相同;不看V时极性交替;V与V之间极性交替;

4、统一确定极性:第一个非0符一般取-1,之后,根据前一个非0符极性,V取同,1取反;

这个照片是我当时记的一些笔记,大家可以参考一下(不一定完全对啊)

HDB3的解码就更简单了。

1、把原来的取代节(4个连零)找到即可,若3连"0"前后非零脉冲同极性,则将最后一个非零元素译为零,如+1000+1 就应该译成"10000",否则不用改动;若2连 "0"前后非零脉冲极性相同,则两零前后都译为零,如 -100-1,就应该译为0000,否则也不用改动.

2、再将所有的-1变换成+1后,就可以得到原消息码。

2. 用verilog设计HDB3 编码及其解码电路

一共分为4个模块

1、插V模块

2、插B模块

3、极性转换模块

4、译码模块

编码模块就占了3个,可想而知有多复杂了

这个具体代码大家就去我的资料里面下载吧,并不是我自己写的代码,而是我之前在一本书里面看到的(《Verilog HDL设计与实战》),这本书讲了很多的用Verilog编程实例,最重要的是,还有代码,比起光讲理论的书好多了

我上传的文档是关于HDB3的代码部分,里面也会有我当时学习的一些笔记啥的,就献丑了(因为里面有一些自己的笔记啥的,所以就标了1E币)

刚刚试了一下把《Verilog HDL设计与实战》书上传,但是超过了300M,等我试试把我找到的配套的视频和代码看看能不能传上去,视频主要是对《Verilog HDL设计与实战》每一章内容的讲解,当然也包括HDB3的了。

附:

用verilog设计HDB3 编码及其解码电路的学习资料

《VerilogHDL设计与实战》配套视频教程和代码

/5

/5

文章评论(0条评论)

登录后参与讨论