代码;

module muxtwo(out,a,b,sl);

input a,b,sl;

output out;

reg out;

always@(sl or a or b)

if(!sl) out=a;

else

out=b;

endmodule

//`include “muxtwo.v”

module t;

reg ain, bin, select;

reg clock;

wire outw;

initial //把寄存器变量初始化为一确定值

begin

ain = 0;

bin = 0;

select =0;

clock = 0;

end

always #50 clock = ~clock; //产生一个不断重复的周期为100的时钟信号clock

always @(posedge clock)

begin // {$random} 为系统任务,它会产生一个随机数

ain = {$random}%2; // 产生随机的位信号流ain ,%2为做模2运算

#3 bin = {$random}%2; // 延迟3个时间单位后产生随机的位信号流bin

end

always #10000 select = !select;

//产生周期为10000个单位时间的选通信号变化

muxtwo m (.out (outw), .a(ain), .b(bin), .sl(select));

/* 实例引用多路器,并加入测试信号流,以观察模块的输出 out。其中

muxtwo是已经定义的(行为的或结构的)模块,m表示在本测试模块

中有一个名为m的muxtwo的模块,其四个端 口分别为:

.out( ) , .a( ), .b( ), .sl( ),

“.”表示端口,后面紧跟端口名,其名称必须与muxtwo模块定义的

端口名一致,小括号内的信号名为与该端口连接的信号线名,可以用

别的名,但必须在本模块中定义,说明其类型。 */

endmodule

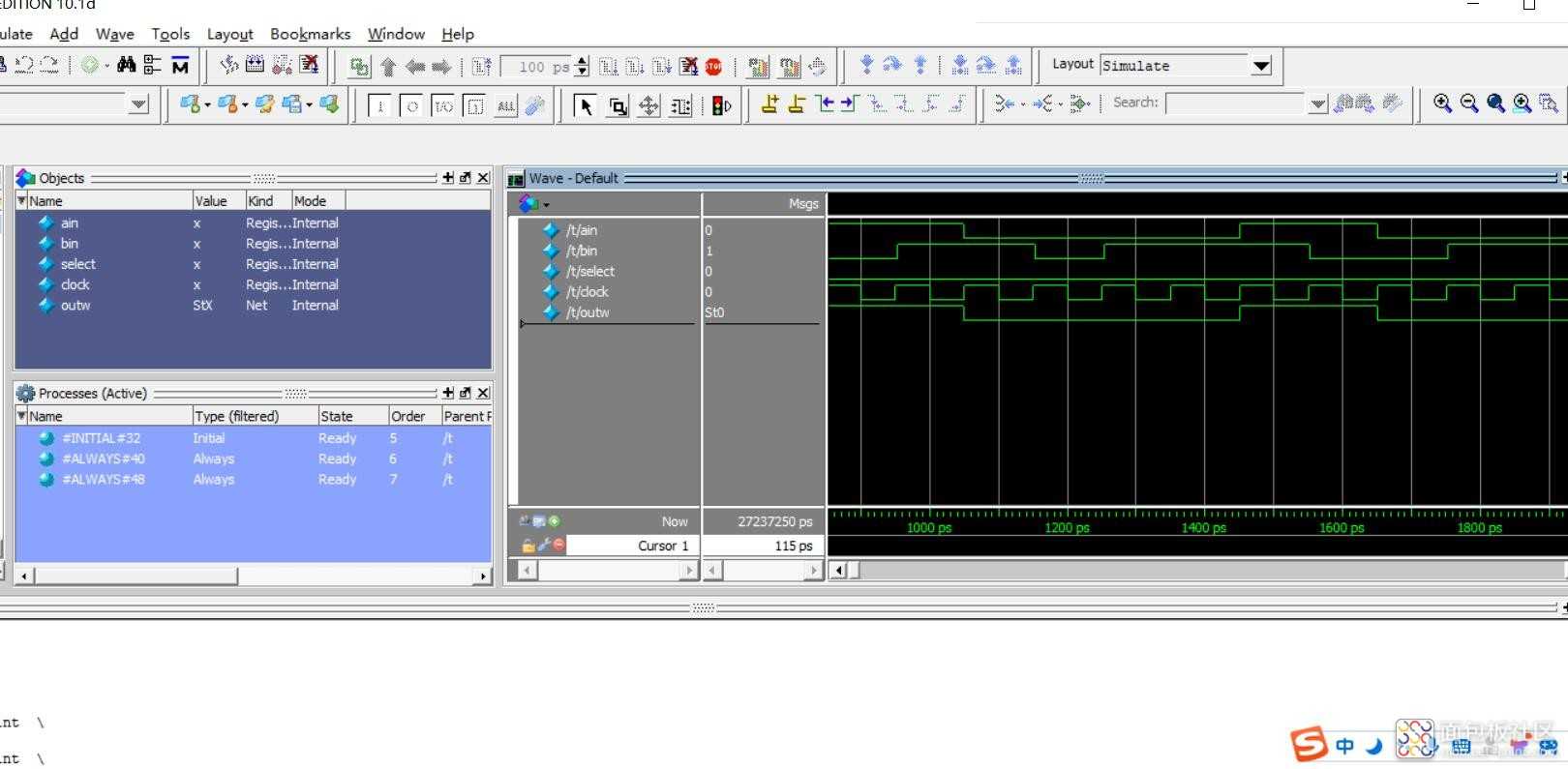

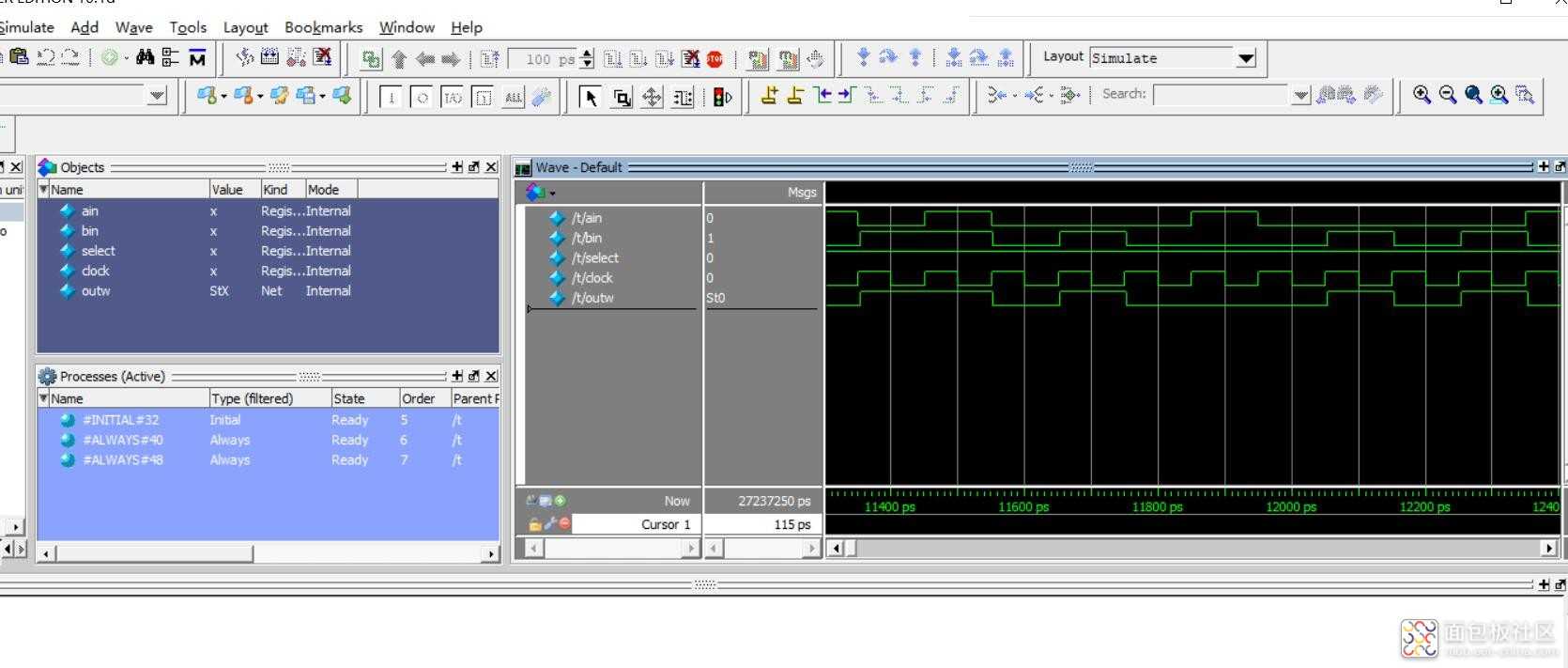

仿真效果:

/4

/4

文章评论(0条评论)

登录后参与讨论