Vivado+LED

官方教学视频链接地址https://www.bilibili.com/video/BV1JJ411u77d?p=2

本次的任务主要是:1.通过Vivado来点亮开发板上的灯 2.了解通过Vivado从新建项目到实际程序运行的整个步骤

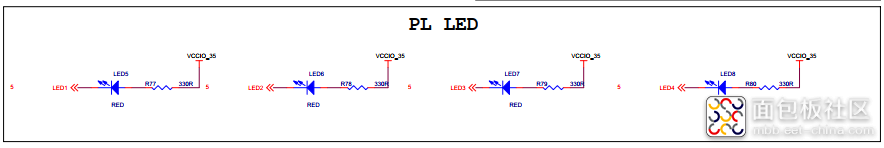

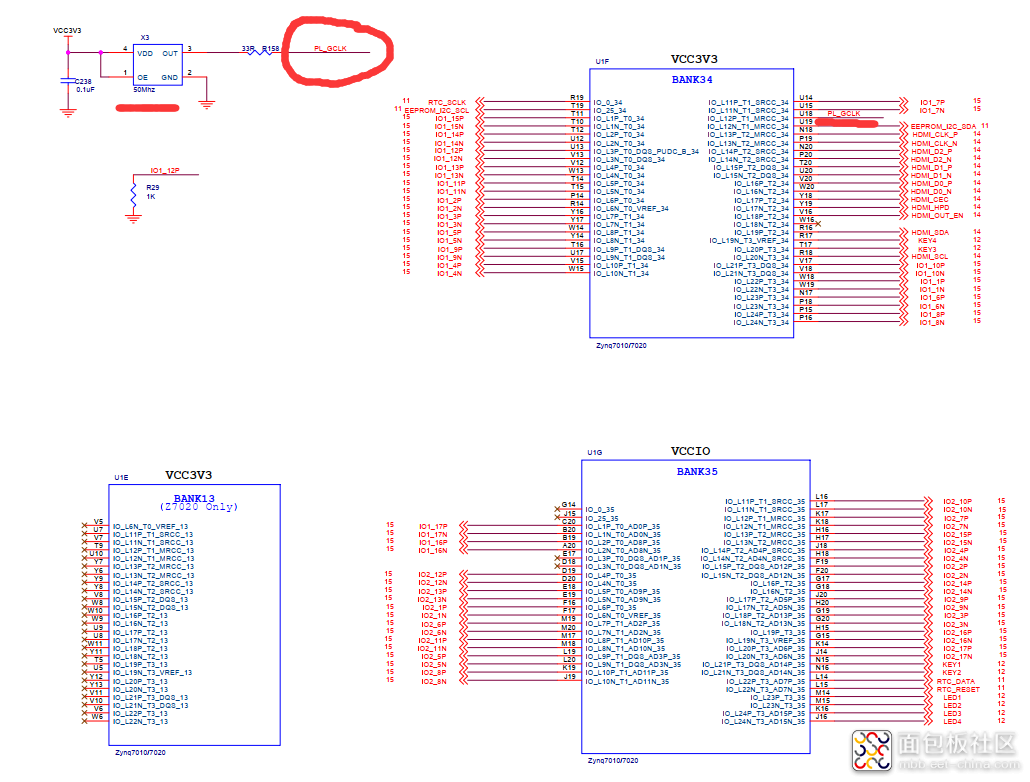

先上原理图

上图是AX7020开发板上对应LED的原理图,下面那张图是LED对应FPGA的管。

上图中有一个细节,即LED的前缀:PL。那么这个PL是什么呢?引用博文https://blog.csdn.net/the_time_runner/article/details/103153261中对PL的定义:PL(Programmable Logic)可编程逻辑,就是FPGA部分

步骤1:打开Vivado(注非Vivado HLS)确保打开后界面如下:

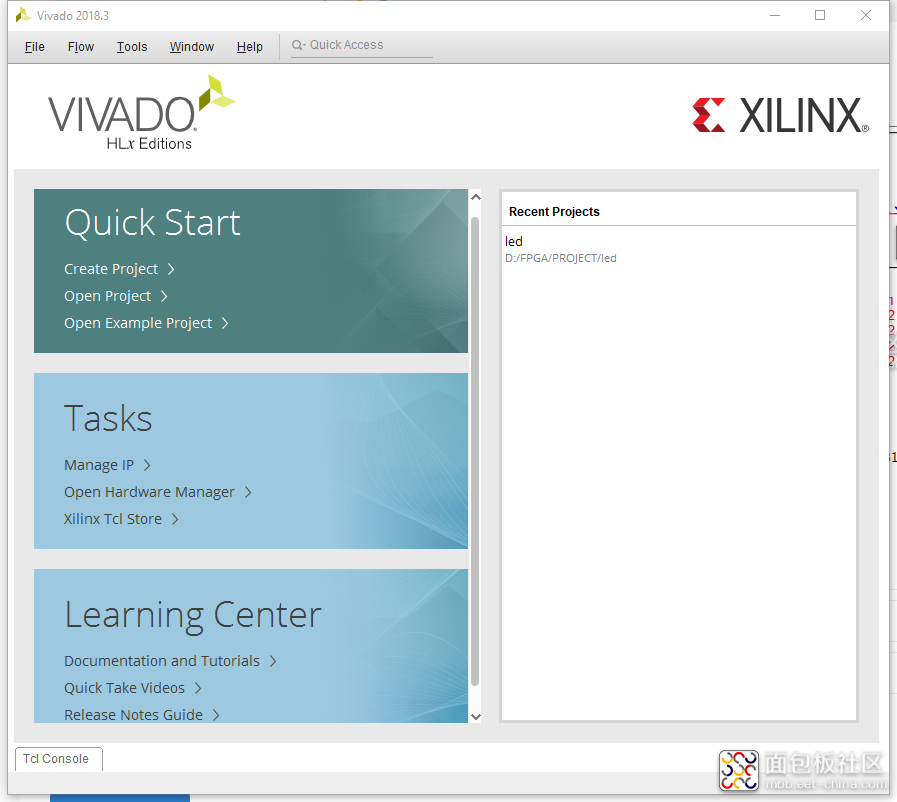

步骤2:根据视频的向导,最后新建的工程如下(具体步骤请参考视频)

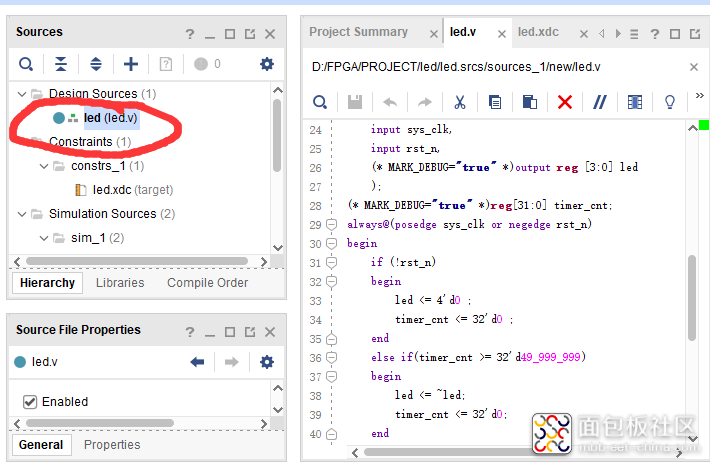

步骤3:添加设计文件

在视频中并没有很详细的给到这段代码,实际上这个文件的路径在:...\AX7020_2017.4.1\course_s1_fpga\01_led\led.srcs\sources_1\new

附上其代码(当然教学方可能是想让大家亲自码一下代码加深一下印象)

timescale 1ns / 1ps

module led(input sys_clk,input rst_n,(* MARK_DEBUG="true" *)output reg [3:0] led);(* MARK_DEBUG="true" *)reg[31:0] timer_cnt;always@(posedge sys_clk or negedge rst_n)beginif (!rst_n)beginled <= 4'd0 ;timer_cnt <= 32'd0 ;endelse if(timer_cnt >= 32'd49_999_999)beginled <= ~led;timer_cnt <= 32'd0;endelsebeginled <= led;timer_cnt <= timer_cnt + 32'd1;endend////Instantiate ila in source file//ila ila_inst(// .clk(sys_clk),// .probe0(timer_cnt),// .probe1(led)// );endmodule复制代码 步骤4:RTL ANALYSIS

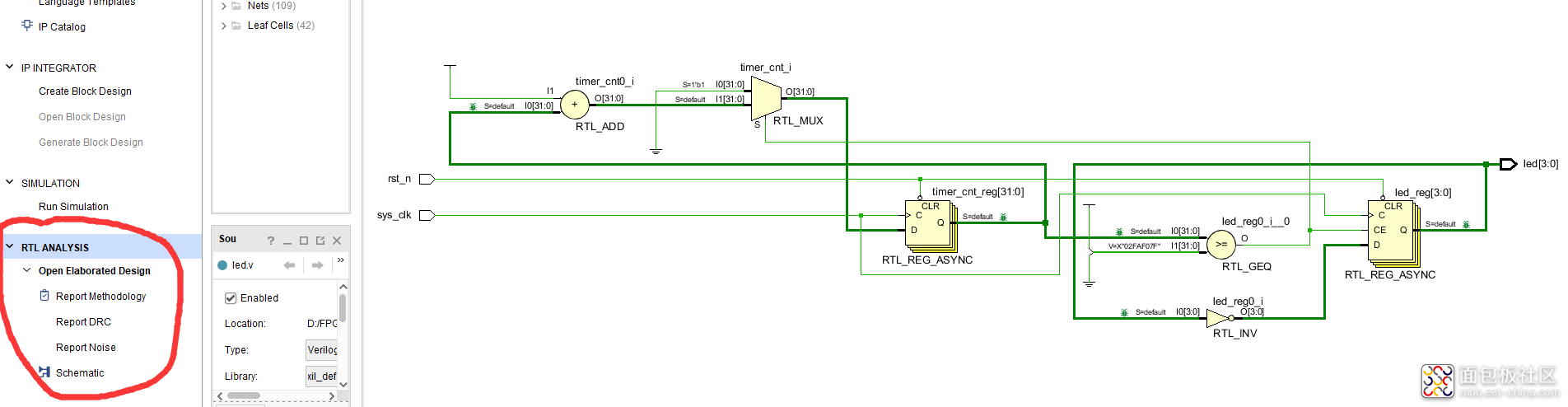

RTL 原理图

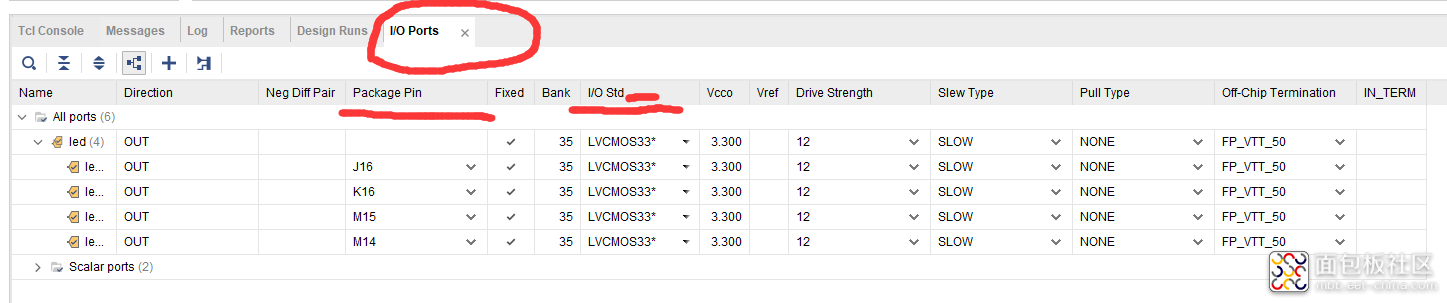

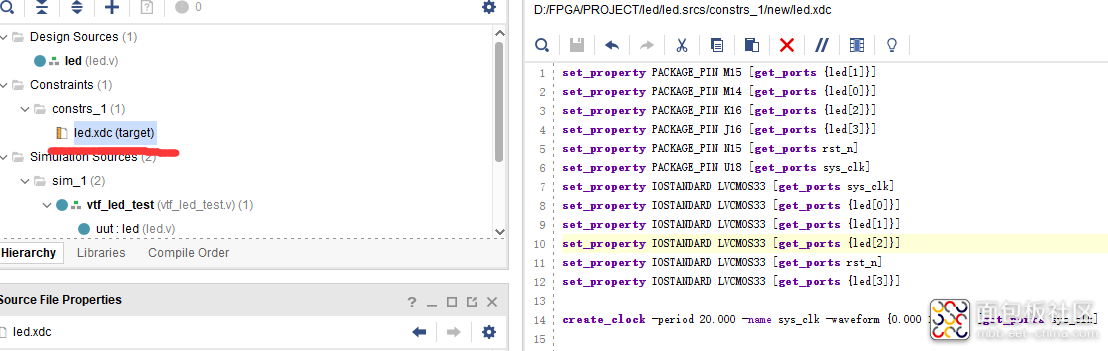

步骤5:IO PORT绑定

部分特性:IO引脚、时钟、电平标准

注意:关于时钟的设置,在原理图中如下,其对应了全局时钟(MRCC),且其频率被固定为50MHz

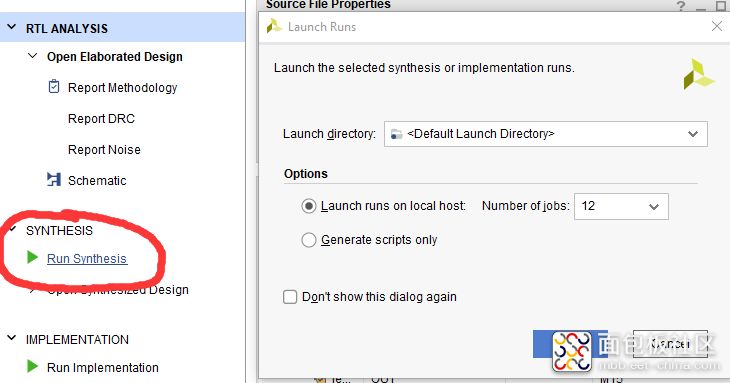

步骤6:Run Synthesis

步骤7:时序约束

具体的内容可以参考博文:https://cloud.tencent.com/developer/article/1528865

https://blog.csdn.net/k331922164/article/details/48687161

https://blog.csdn.net/u012176730/article/details/54412323

通常来说时序约束是指在高速的数据传输中,为了保障数据高效传输且不出错来使用的。

按照本次的教程,主要的约束为时钟信号的频率为50MHz,生成后会反映在led.xdc文件下

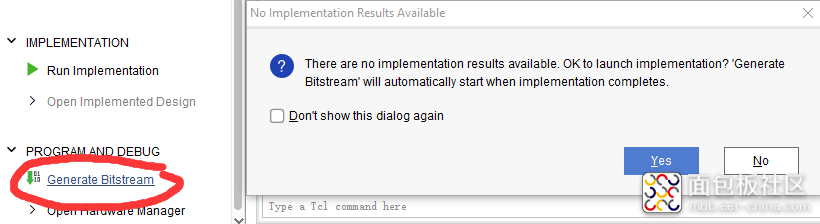

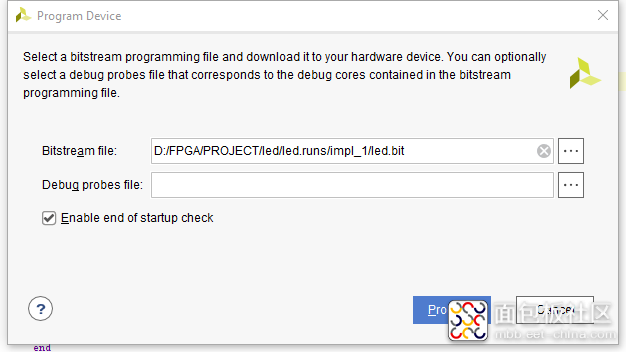

步骤8:Generate Bitstream :运行生成比特流文件

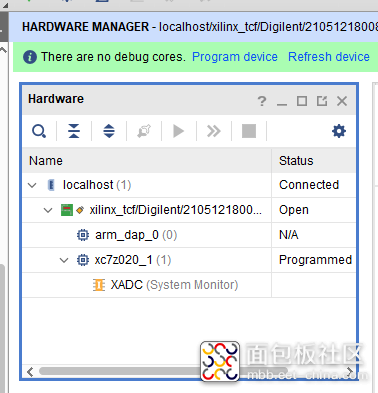

步骤9:实际测试(USB线需要接在开发板的JTAG上,这样Vivado才能识别到设备) 步骤10:程序下载

该步骤结束后就可以看到LED灯的闪烁啦

实际上接下来的步骤,有一个专题即专门讲到FPGA内嵌的逻辑分析仪,将在后续单独拿出来说明

/5

/5

文章评论(0条评论)

登录后参与讨论