我从之前就关注一个工程师分享有关于FPGA的资料,陆陆续续也记录收藏了不少,这次分享给大家共同学习和进步吧

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

引言:FFT(快速傅里叶变换)在雷达信号处理、图像处理、无线通信等行业有着广泛的应用。本文及后续几篇文章,我们针对Xilinx的FFT IP核v9.0提供详细介绍。本文作为开篇,介绍以下内容:

Xilinx FFT IP核的特性

Xilinx FFT IP核输入输出接口介绍

1.Xilinx FFT IP核特性

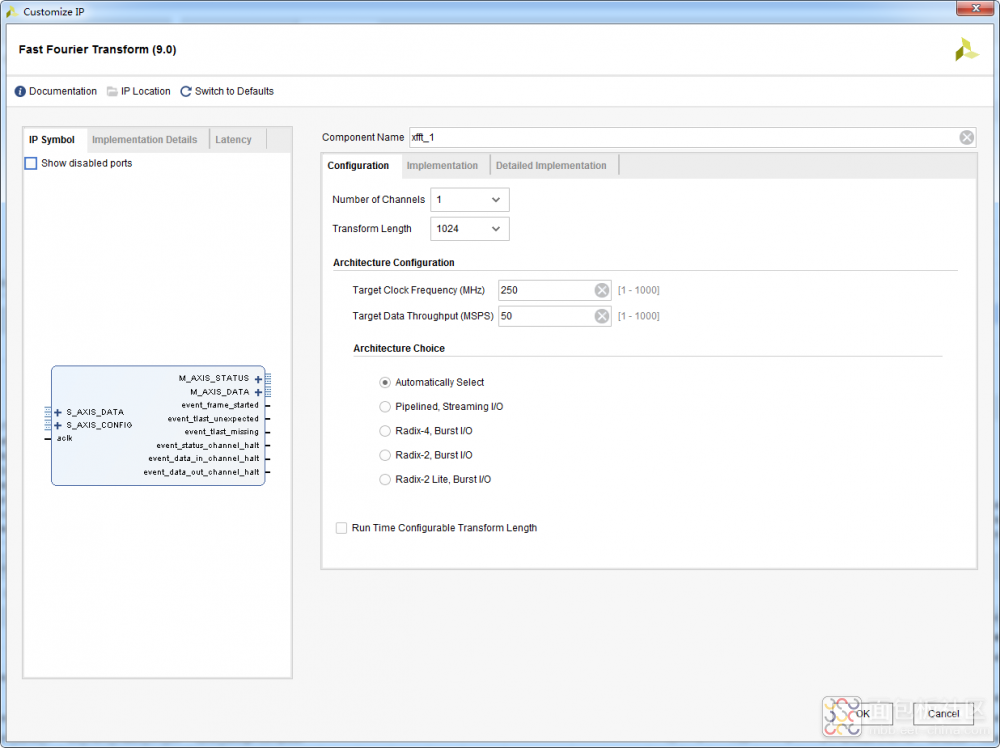

图1、Xilinx FFT IP核

Xilinx®LogiCORE™ IP快速傅立叶变换(FFT)核实现了Cooley-Tukey-FFT算法,这是计算离散傅立叶变换(DFT)的有效方法。该IP核支持以下特性:

正向和反向复数FFT(FFT和IFFT),实时可配置;

转换点数N = 2m,m = 3~16

数据采样精度bx = 8~34

相位因子精度bw = 8~34

算法类型:

未缩放(全精度)定点

缩放定点

块浮点

定点

或浮点接口

舍去或截断处理

数据和相位因子存储可以选择BRAM或者

分布式RAM

缩放定点核支持运行时可配置缩放

输出自然序或者倒序

可选的循环前缀插入

四种架构,支持资源和转换时间权衡

AXI4-Steram接口

2.FFT IP核概述

该IP核支持N点FFT或者IFFT计算,N为2m,m取值3~16。

对于定点输入,输入数据为N个复数向量,表示双路bx-bit二进制补码,即实部和虚部都为bx-bit二进制补码,bx = 8~34,相似地,相位因子bw也为8~34bit位宽。

对于单精度浮点输入,输入N个复数向量,表示双路32-bit浮点数据,相位因子为24或者25bit定点数。

FFT计算支持三种算法选项:

全精度不缩放算法

定点缩放,用户可以提供缩放因子

块

浮点

实时调整缩放

所有的片上使用的存储器可以是块RAM(BRAM)或者分布式RAM(逻辑资源实现)。FFT输入数据可以是自然序方式,输出可以选择自然序或者倒序输出。倒序输出占用的资源更多一些。

转换点数N、正向或反向转换,缩放因子和循环前缀长度都是实时可配置的,转换类型(FFT或IFFT)、缩放因子和循环前缀长度可以在帧间进行改变。改变转换点数N需要复位IP核。

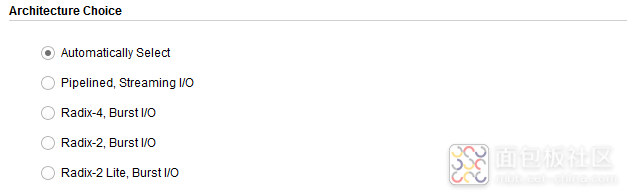

FFT核提供四种可选的算法:流水线I/O、Radix-4突发I/O、Radix-2突发I/O和Radix-2 Lite I/O。

图1、FFT IP核算法选择

3.算法概述

FFT核使用Radix-4和Radix-2分解计算DFT。对于突发I/O架构,使用DIT算法,DIF算法用于流水线I/O架构。当使用Radix-4分解时,N点FFT包含log4(N)级蝶形运算,每级包含N/4个Radix-4蝶形运算。如果N不是4的幂,则需要额外的Radix-2级来组合运算。类似,对于N点FFT使用Radix-2分解运算包含log2(N)级运算,每级包含N/2个Radix-2蝶形运算。

逆FFT(IFFT)是通过共轭对应的的FFT的相位因子来计算的。

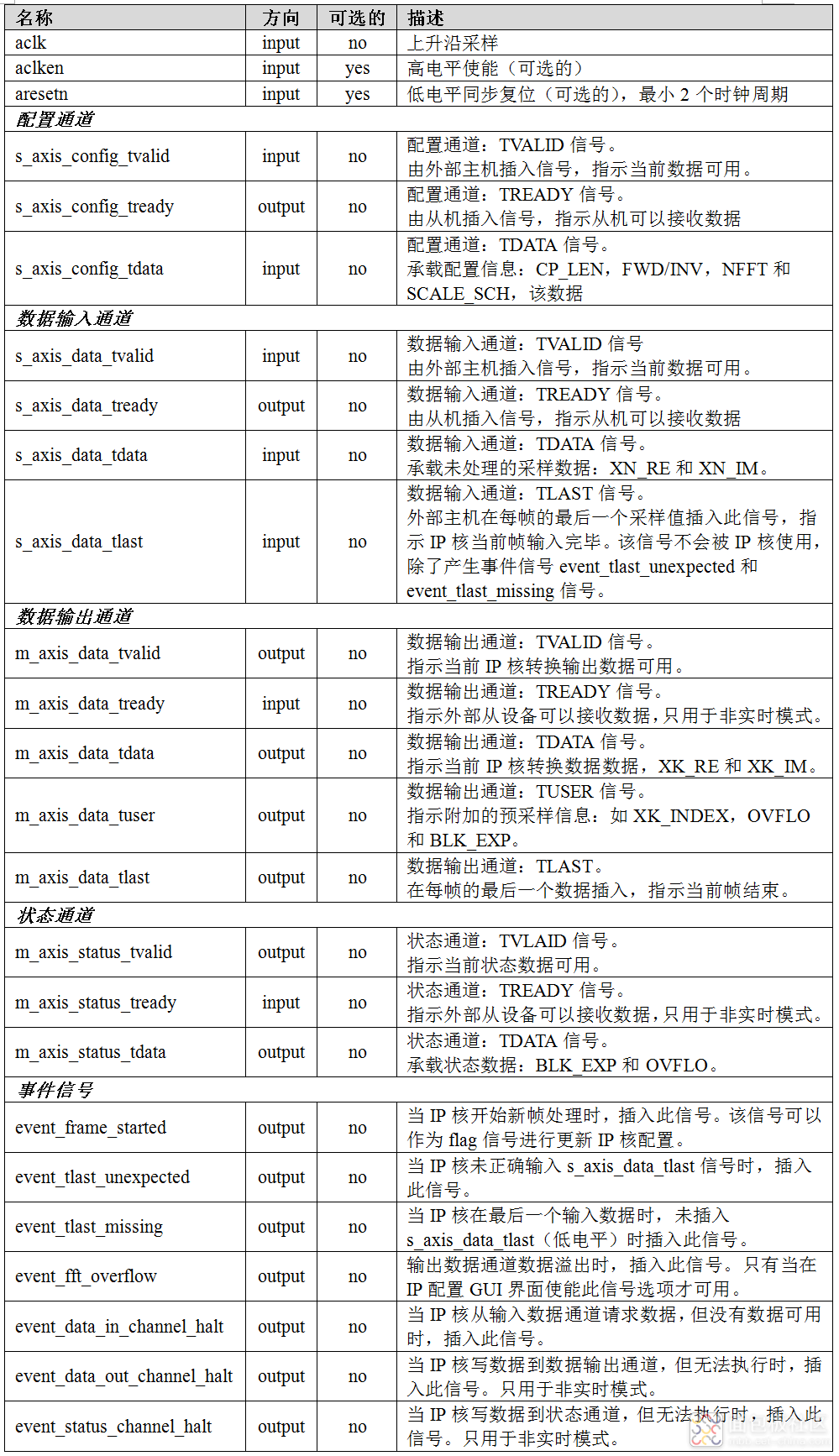

4.FFT IP核接口介绍

图2、FFT IP核接口介绍

/3

/3

文章评论(0条评论)

登录后参与讨论