PCI桥规范定义了透明桥的实现规则,本篇在第2.3.1节中详细介绍了这种桥片。通过透明桥,处理器系统可以以HOST主桥为根节点,建立一颗PCI总线树,在这个树上的PCI设备共享同一个PCI总线域上的地址空间。

但是在某些场合下PCI透明桥并不适用。在图2‑15所示的处理器系统中存在两个处理器,此时使用PCI桥1连接处理器2并不利于整个处理器系统的配置与管理。我们假定PCI总线使用32位地址空间,而处理器1和处理器2所使用的存储器大小都为2GB,同时我们假定处理器1和处理器2使用的存储器都可以被PCI设备访问。

此时处理器1和2使用的存储器空间必须映射到PCI总线的地址空间中,而32位的PCI总线只能提供4GB地址空间,此时PCI总线x0的地址空间将全部被处理器1和2的存储器空间占用,而没有额外的空间分配给PCI设备。

此外有些处理器不能作为PCI Agent设备,因此不能直接连接到PCI桥上,比如x86处理器就无法作为PCI Agent设备,因此使用PCI透明桥无法将两个x86处理器直接相连。如果处理器2有两个以上的PCI接口,其中一个可以与PCI桥1相连(此时处理器2将作为PCI Agent设备),而另一个作为HOST主桥y连接PCI设备。此时HOST主桥y挂接的PCI设备将无法被处理器1直接访问。

使用透明桥也不便于解决处理器1与处理器2间的地址冲突,如图2‑15所示的处理器系统,如果处理器1和2都将各自的存储器映射到PCI总线地址空间中,有可能会出现地址冲突。虽然PowerPC处理器可以使用Inbound寄存器,将存储器地址空间映射到不同的PCI总线地址空间中,但是不是所有的处理器都具有这种映射机制。许多处理器的存储器地址与PCI总线地址使用了“简单相等”这种映射方法,如果PCI总线连接了两个这样的处理器,将不可避免地出现PCI总线地址的映射冲突。

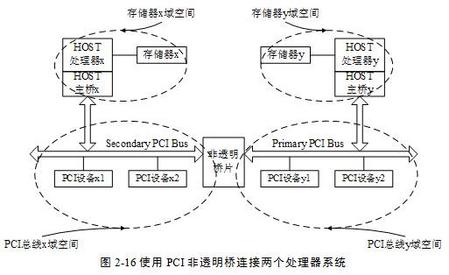

采用非透明桥将有效解决以上这些问题,非透明桥并不是PCI总线定义的标准桥片,但是这类桥片在连接两个处理器系统中得到了广泛的应用。一个使用非透明桥连接两个处理器系统的实例如图2‑16所示。

使用非透明PCI桥可以方便地连接两个处理器系统。从上图中我们可以发现非透明桥可以将PCI总线x域与PCI总线y域进行隔离。值得注意的是,非透明PCI桥的作用是对不同PCI总线域地址空间进行隔离,而不是隔离存储器域地址空间。而HOST主桥的作用才是将存储器域与PCI总线域进行隔离。

非透明PCI桥可以连接两条独立的PCI总线,一条被称为Secondary PCI总线,另一条被称为Primary PCI总线,但是这两条总线没有从属关系,两边是对等的[1]。从处理器x的角度上看,与非透明PCI桥右边连接的总线叫Secondary PCI总线;而从处理器y的角度上看,非透明PCI桥左边连接的总线叫Secondary PCI总线。

HOST处理器x和PCI设备可以通过非透明PCI桥,直接访问PCI总线y域的地址空间,并通过HOST主桥y与访问存储器y;HOST处理器y和PCI设备也可以通过非透明PCI桥,直接访问PCI总线x域的地址空间,并通过HOST主桥x访问存储器x。为此非透明PCI桥需要对分属不同PCI总线域的地址空间进行转换。

目前有许多厂商可以提供非透明PCI桥的芯片,在具体实现上各有差异,但是其基本原理类似,下文以Intel 21555为例说明非透明PCI桥。值得注意的是,在PCIe体系结构中,也存在非透明PCI桥的概念。

Intel 21555非透明PCI桥源于DEC21554[2],并在此基础上做了一些改动。Intel 21555桥片与其他透明桥在系统中的位置相同。如图2‑16所示,这个桥片一边与Primary PCI总线相连,另一边与Secondary PCI总线相连。

在Intel 21555桥片中,包含两个PCI 设备配置空间,分别是Primary PCI总线配置空间和Secondary PCI总线配置空间,处理器可以使用Type 00h配置请求访问这些配置空间。在大多数情况之下,在Primary PCI总线上的HOST处理器管理Primary PCI配置空间;在Secondary PCI总线上的HOST处理器管理Secondary PCI配置空间[3]。

在Intel 21555桥片中,还有一组私有寄存器CSR(Control and Status Register),系统软件使用这组寄存器对非透明桥进行管理并获得桥片的一些信息,这组寄存器可以被映射成为PCI总线的存储器地址空间或者I/O地址空间。

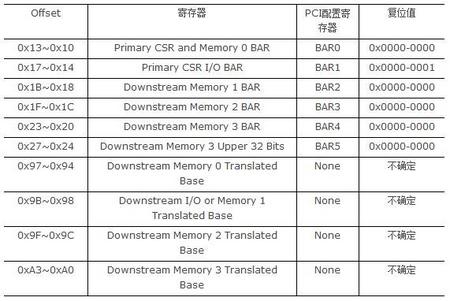

本章仅介绍Primary PCI总线这一边的配置寄存器,Secondary PCI总线的配置寄存器虽然与Primary PCI总线的这些寄存器略有不同,但是基本对等,因此本节对此不做介绍。Primary PCI总线的主要寄存器如表2‑6所示。

表2‑6 Primary PCI总线的配置寄存器

从表2‑6中,我们可以发现Primary PCI总线的这些配置寄存器共分为两组,一组寄存器与PCI设备的配置寄存器的BAR0~5对应,这些寄存器与标准PCI配置寄存器BAR0~5的功能相同;另一组寄存器是Translated Base寄存器,这组寄存器的主要作用是将来自Primary PCI总线的数据访问转换到Secondary PCI总线。

其中BAR0~5寄存器在系统初始化时由Primary PCI总线上的HOST处理器进行配置,配置过程与PCI总线上的普通设备完全相同。只是Intel 21555规定,BAR0只能映射为32位存储器空间。

CSR寄存器可以根据需要映射在BAR0空间中,此时BAR0空间最小为4KB。CSR寄存器也可以根据需要使用BAR1寄存器映射为I/O地址空间,同时BAR1寄存器还可以映射其他I/O空间;BAR2~3只能映射为32位存储器地址空间;而BAR4~5用来映射64位的存储器地址空间。

对于Primary PCI总线,所有BAR0~5寄存器映射的地址空间都将占用Primary PCI总线域,然而这些地址空间中所对应的数据并不在Primary PCI总线域中,而是在Secondary PCI总线域中。Translated Base寄存器实现不同PCI总线域地址空间的转换,Intel 21555将不同PCI总线域地址空间的转换过程称为“地址翻译”。

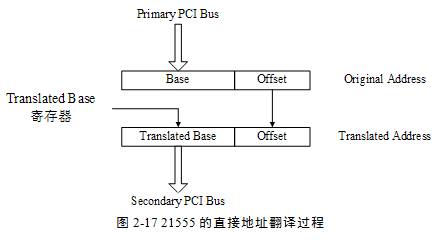

Intel 21555支持两种地址翻译方法,一个是直接地址翻译,一个是查表翻译。Primary PCI总线的BAR空间只支持直接地址翻译,而Secondary PCI总线的Memory 2 BAR空间支持查表翻译,本节仅介绍直接地址翻译方法,对查表翻译有兴趣的读者请阅读Intel 21555的数据手册[4]。直接地址翻译过程如图2‑17所示。

当Primary PCI总线对非透明桥21555的BAR0~5地址空间进行数据请求时,这个数据请求将被转换为对Secondary PCI总线的数据请求。Translated Base寄存器将完成这个地址翻译过程,下节将结合实例说明这个直接地址翻译过程。

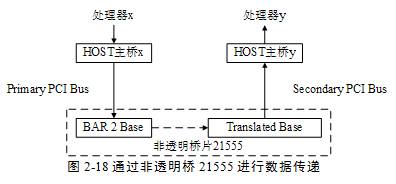

下文以图2‑16中处理器x访问处理器y存储器地址空间的实例,说明非透明桥21555如何将PCI总线x域与PCI总线y域联系在一起。

处理器x需要访问处理器y的存储器空间之前,需要做一些必要的准备工作。

(1) 首先确定由哪一个BAR寄存器空间映射处理器y的存储器地址空间。本节假定使用BAR2寄存器映射处理器y的存储器地址空间。

(2) BAR2寄存器使用Downstream Memory 2 Translated Base寄存器,将来自Primary PCI总线的访问转换为对Secondary PCI总线地址空间的访问。其中Downstream Memory 2 Translated Base寄存器可以由处理器x或者处理器y根据需要进行设置。

假定处理器x和y的HOST主桥使用“直接相等”策略,建立存储器域与PCI总线域间的映射;而处理器x使用BAR2地址空间访问处理器y存储器空间0x1000-000~0x1FFF-FFFF;处理器x的系统软件事先将BAR2寄存器设置完毕。处理器x访问处理器y的这段存储器空间的步骤如下,读者可参考图2‑18理解这一步骤。

(1) 首先处理器x访问在处理器x域中,且与非透明桥的BAR2空间相对应的存储器地址空间。

(2) HOST主桥将进行存储器域到PCI总线域的转换,并将这个请求发送到Primary PCI总线上。

(3) 非透明桥发现这个数据请求发向BAR2地址空间,则接收这个数据请求,并在桥片中暂存这个数据请求。

(4) 非透明桥根据Downstream Memory 2 Translated Base寄存器的内容,按照图2‑17所示的规则进行地址转换。假设Downstream Memory 2 Translated Base寄存器的基地址被预先设置为0x1000-0000,大小为256MB(这个物理地址属于处理器y的主存储器地址空间)。

(5) 经过非透明桥的转换后,这个数据请求将穿越非透明桥,从Primary PCI总线域进入Secondary PCI总线域,然后访问处理器y的基地址为0x1000-0000的存储器区域。

(6) 处理器y的HOST主桥接收这个存储器访问请求,并最终将数据请求发向处理器y的存储器中。

非透明桥21555除了可以支持存储器到存储器之间的数据传递,还支持PCI总线域到存储器域,以及PCI总线域之间的数据传递,此外非透明桥21555还可以通过I2O和Doorbell寄存器进行Primary PCI总线与Secondary PCI总线之间的中断信号传递。本节对这部分内容不做进一步介绍。

非透明桥有效解决了使用PCI总线连接两个处理器存在的问题,因而得到了广泛的应用。在PCIe体系结构中,也存在非透明PCI桥的概念。如在PLX的Switch芯片中,各个端口都可以设置为非透明模式,

本章介绍了在PCI总线中使用的桥,包括HOST主桥和PCI桥,并较为详细介绍了如何使用这些桥访问PCI设备的配置空间。

其中HOST主桥并不在PCI总线规范的约束范围内,不同的处理器可以根据需要设计出不同的HOST主桥。本章更加侧重介绍PowerPC处理器使用的HOST主桥,在该主桥的设计中,提出了许多新的概念,并极大促进了PCI总线的发展,在这个桥片中出现的许多新的思想被PCI V3.0总线规范采纳。

在PowerPC处理器的HOST主桥中,明确了存储器域与PCI总线域的概念。而区分存储器域与PCI总线域也是本章的书写重点,本书将始终强调这两个域的不同。有些处理器系统并没有明确区分这两个域的差别,因此许多读者忽略了PCI总线域的存在,并错误地认为PCI总线域是存储器域的一部分。

在本章中,还重点介绍了PCI桥的实现机制。在许多较为简单处理器系统中,并不包含PCI桥,但是读者仍然需要深入理解PCI桥这一重要概念。深入理解PCI桥的运行机制,是理解PCI体系结构的重要基础。[1] 有些非透明桥,如DEC21554的两边并不是完全对等的,尤其是在处理64位地址空间时,本文对此不做详细说明。

[2] DEC21554是Digital公司的产品。

[3] Intel 21555非透明桥片两边的HOST处理器都可以访问Primary和Secondary总线的配置寄存器。

[4] 多数半导体厂商提供两类芯片手册,分别是Datasheet和User manual。其中Datasheet偏重硬件电气特性,User Manual侧重芯片使用原理。

/5

/5

文章评论(0条评论)

登录后参与讨论