这次遇到的问题是这样的,由于LDO的电源输出能力有限,同时也是保证可靠性,某些保护电路必须直接电源上,这里需要注释的是,LIMP HOME“

跛行回家”即使我们的5V系统出现了问题,我们也必须保证部分重要的功能能继续工作,因此为了满足这个条件,关键信号的供电只能是直接接电池。

这次第一个出问题的是一个CMOS的与门(HE4000B系列的)。

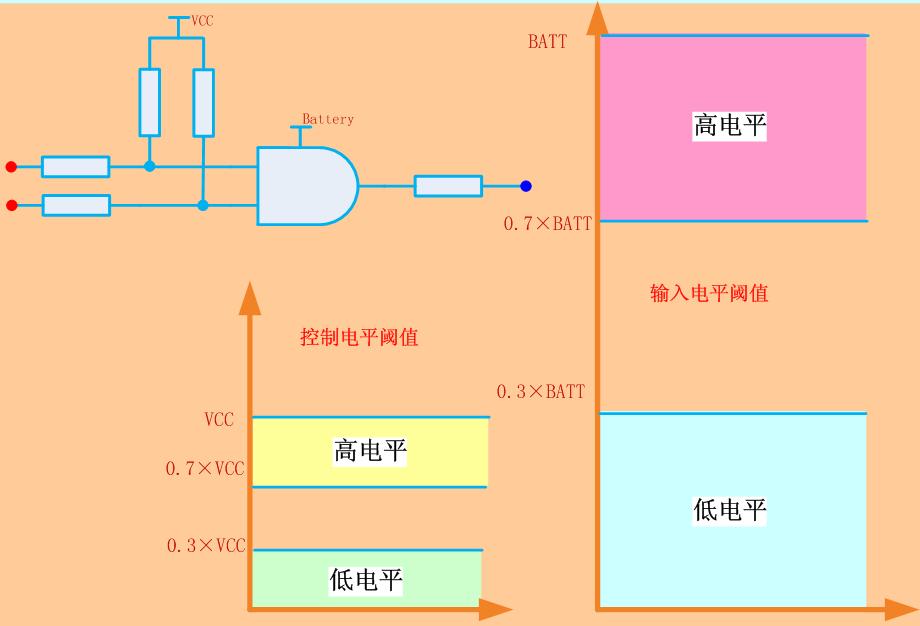

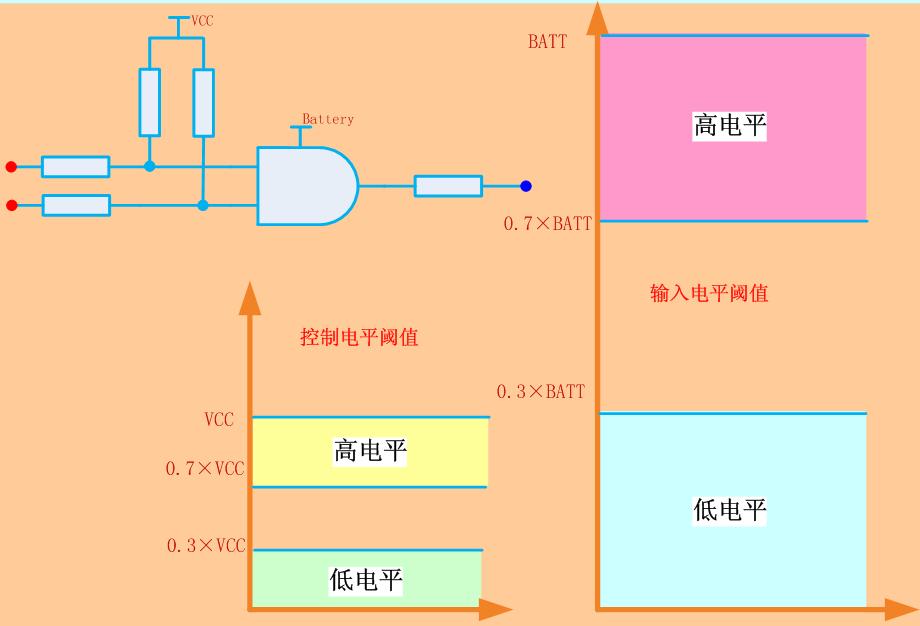

我们的控制信号出自MCU(5V的系统),而与门的系统供电是12V的,因此两个电平不兼容,导致了MCU的高低电平统一被与门CMOS芯片识别成低电平。

我们在设计转换电平的时候,有两个问题需要我们去注意

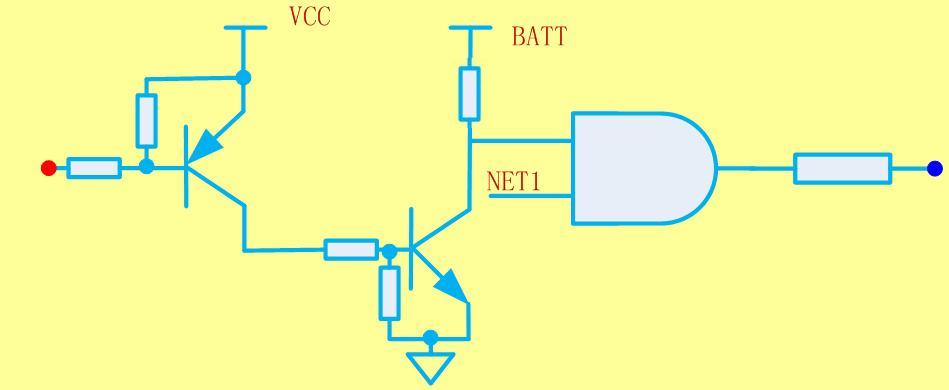

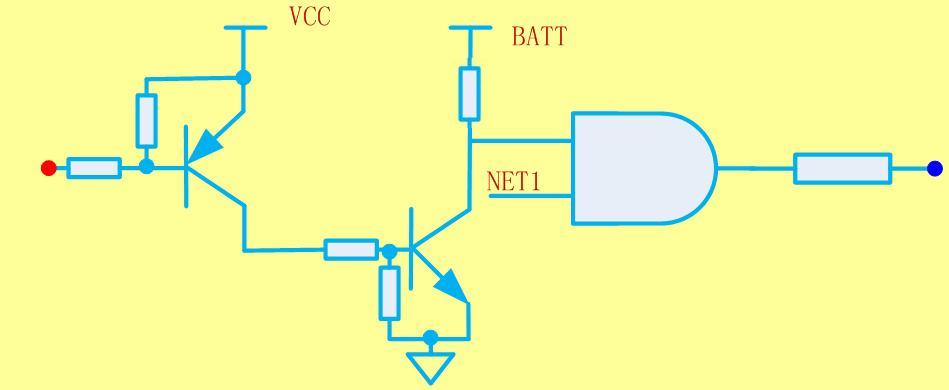

1.要相同的逻辑,不能做成反逻辑

2.在正常状态下,不能允许大的电流(为了符合静态电流的要求)这里设计的是低有效电路,因此在输出高的时候不能出现大的静态电流。

可行的改进设计为:

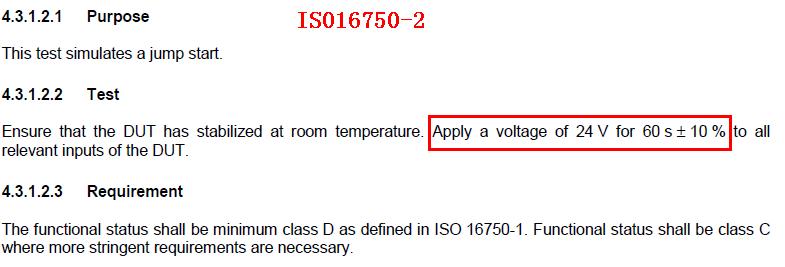

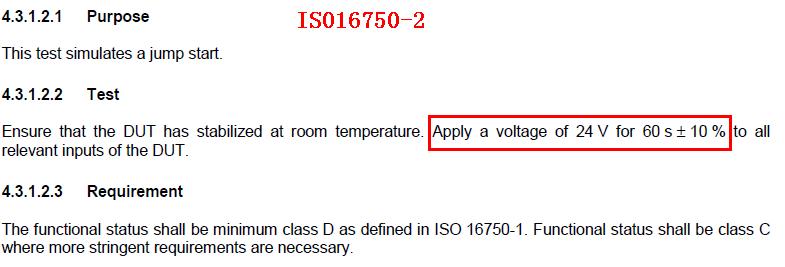

不过一波未平一波又起,由于ISO16750的规定

而我们的与门能够承受的电压为18~20V,这也是所有CMOS的IC的极限电压,因此该芯片华丽的烧毁了(在我们做1分钟的Jump Start实验的时候)

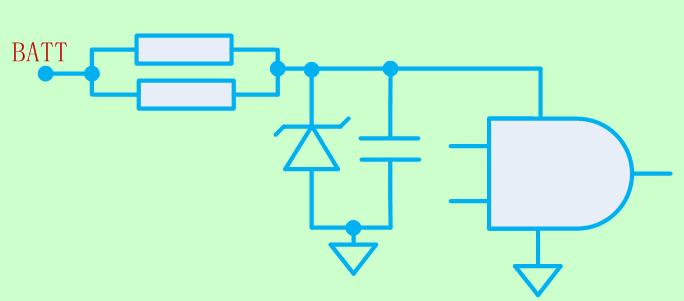

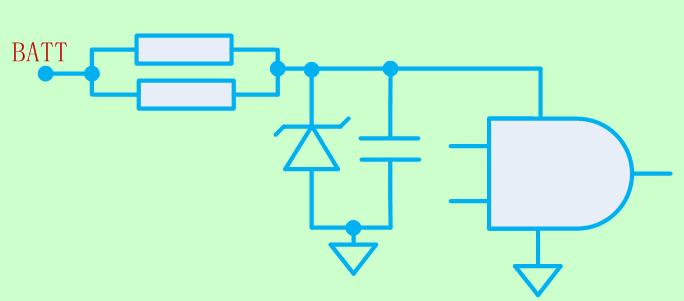

我们的解决方案,加个齐纳管15V钳位

此电阻需要仔细斟酌,因为在24V的时候,有7V的电压在电阻上面,要限制齐纳管的电流防止其过热,同时又要保证CMOS的正常工作电流下,电压不会下降的太厉害。

V.CMOS=V.BATT-R.limit×I.AND

I.zener_max=(24-15)/R.limit

以上需要综合考虑。

/3

/3

文章评论(0条评论)

登录后参与讨论