单片机IO口的驱动能力这是我曾经写过的文章,不过我最近在考虑一个事情。我们可以从书中找出这样一个描述:

扇入系数,是指门电路允许的输入端数目。

一般TTL电路的扇入系数 Nr为1~5,最多不超过8。若芯片输入端数多于实际要求的数目,可将芯片多余输入端接高电平(+5V)或接低电平(GND)。

扇出系数,是指一个门的输出端所驱动同类型门的个数,或称负载能力。

NO=IOLMAX/IILMAX,这是一个通俗的定义一般用在TTL电路的定义中。其中IOLMAX为最大允许灌电流,IILMAX是一个负载门灌入本级的电流。

TTL电路的扇出系数Nc为8~10。

CMOS电路的扇出系数Nc可达20~25。

当然LVTTL和LVCMOS都可进一步验算获得。

Nc表征了门电路的负载能力。

这个是通常的说法,我接下来找些数据来验证以及提出我个人的一些看法。

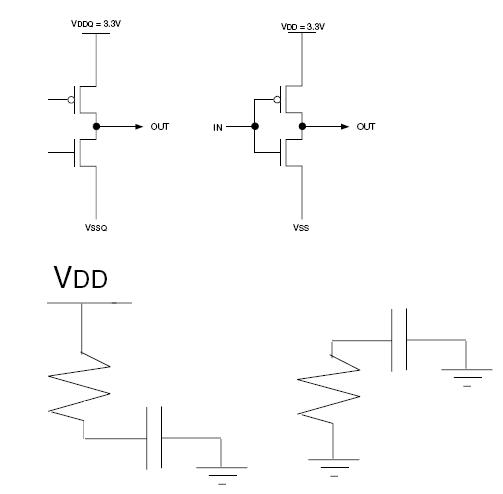

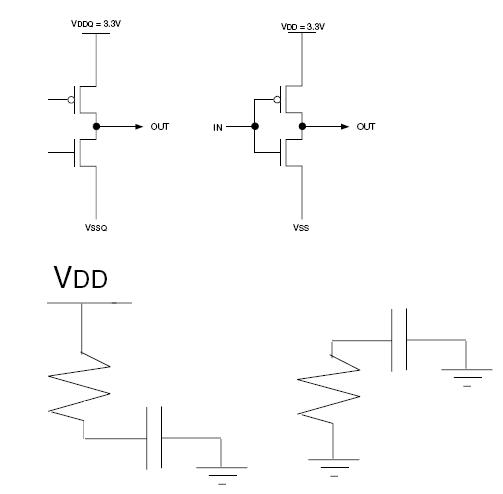

1.TTL電路TTL的验算是比较好弄的,TTL与TTL之间如下图所示:

由于本身晶体管的转换速度有限,因此对于TTL来说,扇入扇出系数无所谓低频和高频而言。

2.CMOSCMOS由不静态功耗较少,因此我们的扇出系数实质上是根据频率有关的。

因此,扇出系数是根据输出波形识别的时序而定的,随着频率的增加,扇出系数越来越小。

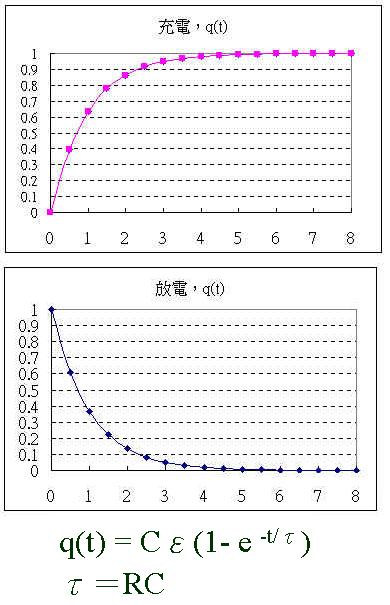

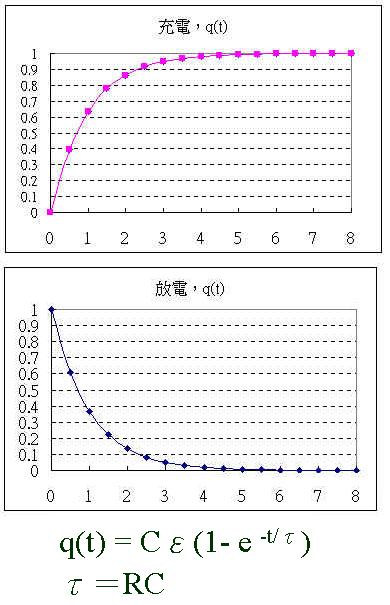

这是因为理论上来说Rdson和Ci都是确定的,根据充放电过程

注意Rdson的能力计算可参考前面的博文

通过计算时间常数,我们可测算

1.10%=>90%的时间,并确认高电平的时间。

2.90%=>10%的时间,并确认低电平的时间。

如果这两个都符合,则可接受。

当然MOS管的输出电容和PCB板的寄生电感和电容,这些因素都会影响实际的效果。

我在以前一般计算静态的输出能力较多,不过按照输出频率的能力则需要进行校验了。在汽车电子中,如果有高速CAN和高速SPI口,则需要注意高速口的充放电电流。

这是因为,我们需要同时确认所有逻辑电源的静态电流,也需要计算逻辑电源上的瞬时电流,这些电流主要是集中与这些高速IO口的充放电电流,如果不注意,则很容易对LDO造成负荷。

当然这点也是一点点想到的,上次Fairchild有个高级经理聊到MOS管的一个案例:

在一定工作状态下的MOS管,随着时间的推移自身逐渐老化,其电压上升和下降率随慢慢下降,也就是边沿不够陡,使得开关功耗大大增加,慢慢使得产品出现热损坏。这个现象确实被证实了,我们的电子模块经过三温三压实验以后,明显比之前的响应速度明显降低。

我们在DATASHEET上的数据,要么是常温下做的,要么是么有经过老化的,有时候觉得按照DATASHEET做设计也是冒很大的风险的。

/4

/4

文章评论(0条评论)

登录后参与讨论