LVDS信号在PCB上的要求<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

1.布成多层板。

有LVDS信号的印制板一般都要布成多层板。由于LVDS信号属于高速信号,与其相邻的层应为地层,对LVDS信号进行屏蔽防止干扰。另外密度不是很大的板子,在物理空间条件允许的情况下,最好将LVDS信号与其它信号分别放在不同的层。例如,对于四层板,通常可以按以下进行布层:LVDS信号层、地层、电源层、其它信号层。

2.LVDS信号阻抗计算与控制。

对于LVDS信号,必须进行阻抗控制(通常将差分阻抗控制在100欧姆)。对于不能控制阻抗的PCB布线必须小于500MIL。这样的情况主要表现在连接器上,所以在布局时要注意将LVDS器件放在靠近连接器处,让信号从器件出来后就经过连接器到达另一单板。同样,让接收端也靠近连接器,这样就可以保证板上的噪声不会或很少耦合到差分线上。LVDS信号的电压摆幅只有350 mV,适于电流驱动的差分信号方式工作。为了确保信号在传输线当中传播时不受反射信号的影响,LVDS信号要求传输线阻抗受控,通常差分阻抗为(100±10)Ω。阻抗控制的好坏直接影响信号完整性及延迟。如何对其进行阻抗控制呢?

① 确定走线模式、参数及阻抗计算。LVDS分外层微带线差分模式和内层带状线差分模式两种,分别如图2、图3所示。通过合理设置参数,阻抗可利用相关阻抗计算软件(如POLAR-SI6000、CADENCE的ALLEGRO)计算也可利用阻抗计算公式计算。

② 走平行等距线。确定走线线宽及间距,在走线时要严格按照计算出的线宽和间距,两线间距要一直保持不变,也就是要保持平行。平行的方式有两种: 一种为两条线走在同一线层(side-by-side),另一种为两条线走在上下相两层(over-under)。一般尽量避免使用后者即层间差分信号,因为在PCB板的实际加工过程中,由于层叠之间的层压对准精度大大低于同层蚀刻精度,以及层压过程中的介质流失,不能保证差分线的间距等于层间介质厚度,会造成层间差分对的差分阻抗变化。困此建议尽量使用同层内的差分。

3.紧耦合原则。

在计算线宽和间距时最好遵守紧耦合的原则,也就是差分对线间距小于或等于线宽。当两条差分信号线距离很近时,电流传输方向相反,其磁场相互抵消,电场相互耦合,电磁辐射也要小得多。

4.走短线、直线。

为确保信号的质量,LVDS差分对走线应该尽可能地短而直,减少布线中的过孔数,避免差分对布线太长,出现太多的拐弯,拐弯处尽量用45°或弧线,避免90°拐弯。

5.不同差分线对间处理。

LVDS对走线方式的选择没有限制,微带线和带状线均可,但是必须注意要有良好的参考平面。对不同差分线之间的间距要求间隔不能太小,至少应大于3~5倍差分线间距。必要时在不同差分线对之间加地孔隔离以防止相互问的串扰。

6.LVDS信号远离其它信号。

对LVDS信号和其它信号比如TTL信号,最好使用不同的走线层,如果因为设计限制必须使用同一层走线,LVDS和TTL的距离应该足够远,至少应该大于3~5倍差分线间距。

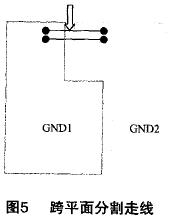

7.LVDS差分信号不可以跨平面分割。

尽管两根差分信号互为回流路径,跨分割不会割断信号的回流,但是跨分割部分的传输线会因为缺少参考平面而导致阻抗的不连续(如图箭头处所示,其中GND1、GND2为LVDS相邻的地平面)。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

8.匹配电阻的精度要求。

对于点到点的拓扑,走线的阻抗通常控制在100Ω,但匹配电阻可以根据实际的情况进行调整。电阻的精度最好是1%~2%。因为根据经验,10%的阻抗不匹配就会产生5%的反射。对接收端的匹配电阻到接收管脚的距离要尽量的靠近,一般应小于<?xml:namespace prefix = st1 ns = "urn:schemas-microsoft-com:office:smarttags" />7mm,最大不能超过12mm。

9.电源地

对收发器的电源和地进行滤波处理,滤波电容的位置应该尽量靠近电源和地管脚,滤波电容的值可以参照器件手册。对电源和地管脚与参考平面的连接应该使用短和粗的连线连接。同时使用多点连接。保证信号的回流路径最短,同时没有相互间的干扰。

在低频(500-600MHZ)时,选用FR-4材料制造,在更高速度的时候选用G-FEK或Teflon来设计生产;用旁路电容旁路所有的电源平面,旁路电容的大小由电源噪声的频谱决定,所选用的电容应该能滤去最大功率的部分(通常在100-300MHZ),典型利用10uF/3V的钽电容;所有电源的VCC-CKIN和VCC-CKOUT管脚应该用0.1、0.01、0.001uF的云母、碰珠或者0805尺寸的贴片电容并行连接进行旁路,这些电容应该放在管脚的下面,另外还要加一个2 .7uF的电容; LVDS的电源和地分层。

AD里面进行LVDS布线的小教程

https://static.assets-stash.eet-china.com/album/old-resources/2009/5/31/b52a925f-a973-434a-95f4-c4c5e73c8488.rar

工程师前辈们写的pcb走线策略

https://static.assets-stash.eet-china.com/album/old-resources/2009/5/31/2e9d3a82-9025-40b8-8dad-6d12574e344a.rar

/1

/1

用户579321 2011-8-16 19:32

用户410463 2011-2-20 11:35