以前设计中将AD的时钟是FPGA使用DCM分频产生的30M,而FPGA内部采集数据的时钟也是使用同一个时钟分频产生的30M,在截取AD采集的数据时没有出现不同步的问题。

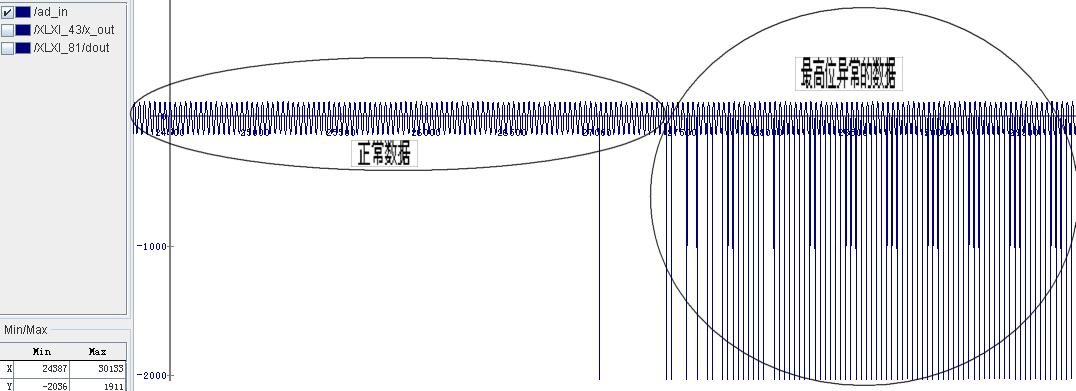

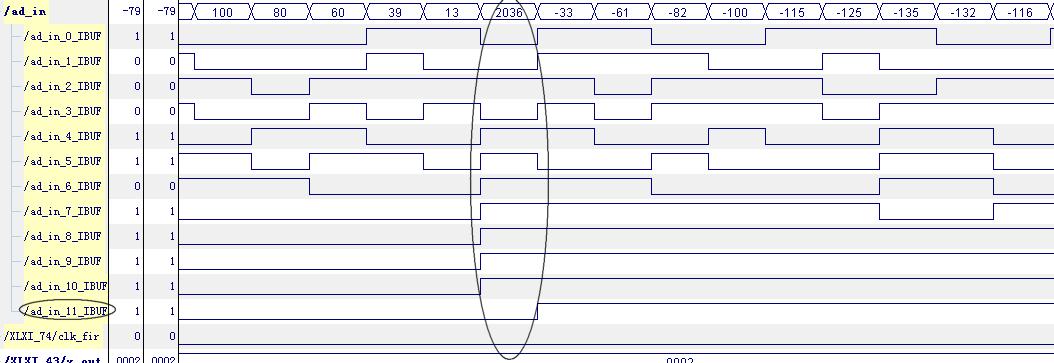

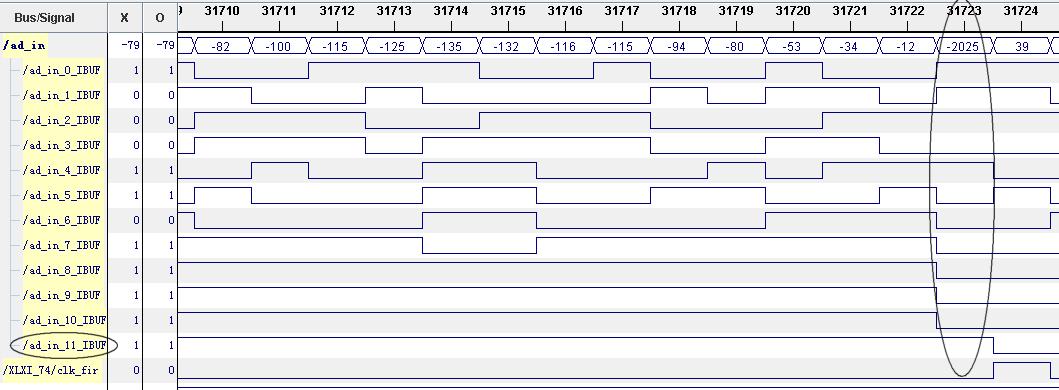

现在由于要提高指标,将AD的时钟换为低抖动的30M晶振,而FPGA内部还是使用一般晶振分频产生的30M做为采集时钟,发现数据偶尔会出现不正常,现象是AD输出数据的最高位与其他位出现了不同步,原来大概估计到了不同步的情况,以为数据出现不同步是FPGA产生的30M时钟的上升沿刚好出现在AD数据输出的亚稳态部分,使用DCM调制输出30M时钟的相位即可,但是实际现象是采样保障了低11位,而最高位没有保证,现象大体如下,大家有什么好一点的办法!!!

错误的采集数据:

/4

/4

bitao1983_395643617 2013-7-12 12:46

用户377235 2013-7-3 08:39