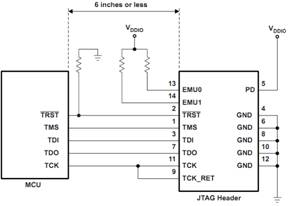

JTAG口:TRST, TCK, TDI, TMS, TDO

JTAG口与DSP距离最好再5cm,最多不超过15cm

1. TRST,有内部下拉。当该引脚不接或拉低将处于功能模式,测试复位信号将被忽略,实际正常操作中应将该引脚经过一推荐2.2K左右的电阻持续拉低电平。P21

2. 2806X无EMU0和EMU1引脚故JTAG口插口处需经4.7K电阻上拉VDDIO该两个引脚(P72)

3. 1,2均是为了抗噪设计,在高噪声环境,TRST的下拉电阻阻值应下调,且在TRST,EMU0,EMU1加装0.1uF的旁路电容;

4. TCK(GPIO38):JTAG测试时钟,有内上拉;

5. TMS:JTAG测试模式选择,含有内上拉

6. JTAG口外形

|

|

|

|

|

|

7. .

/5

/5

文章评论(0条评论)

登录后参与讨论