搞定TimeQuest鞭长莫及的特定路径例外约束

<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

TimeQuest中提供了一些特定时钟域间的例外约束,也提供了一些特定路径间的例外约束,只不过特权同学在实际工程中遇到了特定路径中的特定路径需要例外约束的情况,好像TimeQuest还真无法直接便利的对这种情况的路径进行约束,特权同学就班门弄斧谈一谈自己对这种情况是如何做时序约束的,也许TimeQuest也提供了对这种路径的约束,但是特权同学至今没有看到任何选项或资料提到相关方法。

先从工程的约束需求说起,工程中有两条关键路径sram_addr[0]和sram_addr[1],对他们的输出时序要求很高(为什么这里就不提了,不是讨论的重点)。通常可以按照以下的语句进行约束:

set_output_delay -add_delay -max -clock [get_clocks {VIRLCLK}] 15.500 [get_ports {sram_addr[0]}]

set_output_delay -add_delay -min -clock [get_clocks {VIRLCLK}] 0.000 [get_ports {sram_addr[0]}]

set_output_delay -add_delay -max -clock [get_clocks {VIRLCLK}] 15.500 [get_ports {sram_addr[1]}]

set_output_delay -add_delay -min -clock [get_clocks {VIRLCLK}] 0.000 [get_ports {sram_addr[1]}]

上面的约束其实是覆盖了所有输出到sram_addr[0]和sram_addr[1]的路径。但是在实际设计中对于这两个输出端口相关的路径并非都需要这么紧的约束,也就是说在这个约束中需要有例外约束。开篇也提到了,在TimeQuest中好像没有直接可以做这种路径例外约束的方法,因此下面就要来谈谈如何使用TimeQuest提供的既有的约束方法来处理这种无法直接约束的路径。

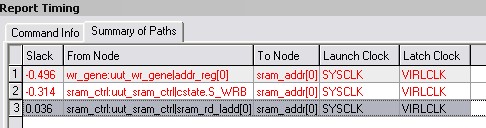

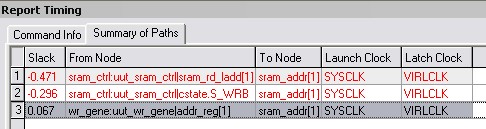

先看在前面的约束语句下,sram_addr[0]所有路径的时序报告如图1,sram_addr[1]的所有路径的时序报告如图2所示。

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

图1

图2

为了和后面的进行例外约束后的报告对比,这里我们看看图2第3条路径的Data required path,如图3所示。

图3

其实从上面的时序报告中可以发现,由于某些路径的过约束,也导致了时序达不到收敛。下面使用了TimeQuest提供的set maximum delay和set minimum delay约束,对前面和sram_addr[0]\sram_addr[1]相关的特定路径做例外约束。

#**************************************************************

# Set Maximum Delay

#**************************************************************

set_max_delay -from [get_registers {sram_ctrl:uut_sram_ctrl|cstate.S_WRB wr_gene:uut_wr_gene|addr_reg[0] wr_gene:uut_wr_gene|addr_reg[1]}] -to [get_ports {sram_addr[0] sram_addr[1]}] 30.000

#**************************************************************

# Set Minimum Delay

#**************************************************************

set_min_delay -from [get_registers {sram_ctrl:uut_sram_ctrl|cstate.S_WRB wr_gene:uut_wr_gene|addr_reg[0] wr_gene:uut_wr_gene|addr_reg[1]}] -to [get_ports {sram_addr[0] sram_addr[1]}] 5.000

先来看时序报告的结果,然后再讨论set maximum delay和set minimum delay约束在时序分析中的影响。

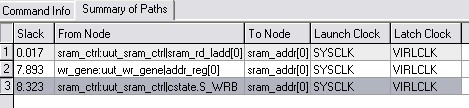

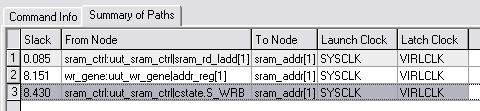

添加例外约束后的sram_addr[0]所有路径的时序报告如图4,sram_addr[1]的所有路径的时序报告如图5所示。

图4

图5

与前面图3相对应的一条Data required path如图6所示。

图6

大家应该都发现了。一方面是这个set maximum delay和set minimum delay约束改变了被约束路径的Data required path分析,使得相应路径的时序要求放宽了。另一方面也使得系统的整体时序性能得到了提高,达到了时序收敛。

再说这个set maximum delay其实就是限定了被约束路径的latch edge time,上面的示例是将特定路径的约束放宽了10ns(30ns-20ns)。而set minimum delay也起到了类似的效果,感兴趣的朋友可以自己做个实例分析下。

用户1679385 2015-4-20 13:15

用户1749260 2015-4-18 19:34

用户1757044 2015-4-17 10:31

用户1620464 2010-12-24 22:14

asus119_412419641 2010-5-5 00:28