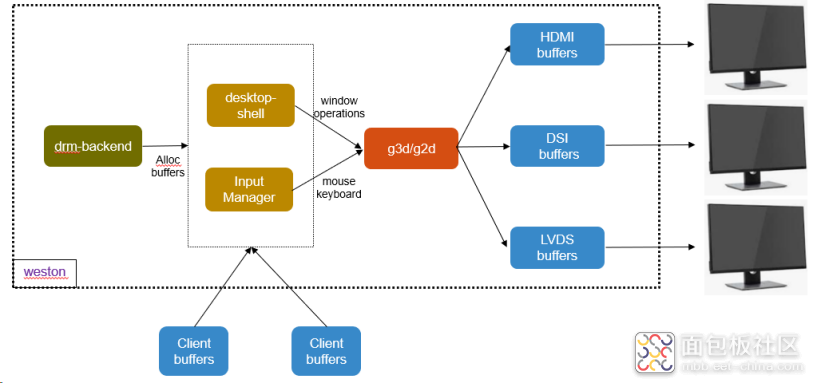

B y Toradex 秦海 1). 简介 NXP i.MX8MP ARM SoC 支持 3 路 Display Controller 分别提供 DSI/HDMI/LVDS 显示输出,在 Yocto Linux BSP 下采用 Wayland Backend 基于 DRM subsystem 显示驱动,前端默认基于 Weston Compositor 。因此在默认情况下连接多个屏幕的显示输出是如下 Extended 模式: 而为了实现多屏幕 Clone Mode 显示,就需要修改显示 buffer 输出模式如下: 本文就基于上述显示输出 pipeline 修改测试 i.MX8MP 多屏 Clone Mode ,本文所涉及的方法和实际修改代码均来自于如下 NXP 论坛文档,本文仅进行测试演示示例。 https://community.nxp.com/t5/i-MX-Graphics-Knowledge-Base/Weston-clone-mode-on-i-MX8MPlus/ta-p/1791853 本文所演示的平台来自于 Toradex Verdin i.MX8MP 嵌入式平台 。 2. 准备 a). Verdin i.MX8MP ARM 核心版配合 Dahlia 载板, 并连接调试串口用于测试 。 b). Dahlia 载板分别由 DSI-HDMI 转接卡和 native HDMI 两个接口连接两台 HDMI 显示器以便于进行多屏显示测试。 3). 修改部署方法之一:通过 Yocto 编译部署 a). 考虑可维护性和易用性,此方法为推荐方法。 b ). 首先 参考 这里 说明创建 Yocto /Openembedded 编译 框架 , 当前最新版本是对应于 Toradex Yocto Linux BSP 7.x 版本的 scarthgap-7.x.y branch 。 c). 创建定制化 layer meta-customer-demos ,用于添加 Weston 源码修改相关 patch 文件。 --------------------------------------- $ mkdir -p ../oe_core/layers/meta-customer-demos/conf $ cd .../oe_core/layers/meta-customer-demos/conf ### create layer.conf file ### # We have a conf and classes directory, append to BBPATH BBPATH .= ":${LAYERDIR}" # We have recipes-* directories, add to BBFILES BBFILES += "${LAYERDIR}/recipes-*/*/*.bb ${LAYERDIR}/recipes-*/*/*.bbappend" BBFILE_COLLECTIONS += "customer-demos" BBFILE_PATTERN_customer-demos = "^${LAYERDIR}/" BBFILE_PRIORITY_customer-demos = "24" # Let us add layer-specific bbappends which are only applied when that # layer is included in our configuration BBFILES += "${@' '.join('${LAYERDIR}/%s/recipes*/*/*.bbappend' % layer \ for layer in BBFILE_COLLECTIONS.split())}" # Add layer-specific bb files too BBFILES += "${@' '.join('${LAYERDIR}/%s/recipes*/*/*.bb' % layer \ for layer in BBFILE_COLLECTIONS.split())}" LAYERDEPENDS_customer-demos = " \ core \ yocto \ openembedded-layer gnome-layer multimedia-layer networking-layer \ " LAYERSERIES_COMPAT_customer-demos = "hardknott honister kirkstone scarthgap" --------------------------------------- d). 在定制化 layer meta-customer-demos 下面添加 Weston bbappend 文件,应用相应的 patch 文件 --------------------------------------- $ cd .../oe_core/layers/meta-customer-demos/ $ mkdir -p recipes-graphics/wayland/files $ cd recipes-graphics/wayland ### cteate weston_12.0.4.imx.bbappend file ### FILESEXTRAPATHS:prepend := "${THISDIR}/files:" SRC_URI += " \ file://0001-weston-imx-12.0.4-LF6.6.52_2.2.0-clone-mode-8MP.patch \ " --------------------------------------- e). 将如下 0001-weston-imx-12.0.4-LF6.6.52_2.2.0-clone-mode-8MP.patch 补丁文件复制到 “ .../oe_core/layers/meta-customer-demos/recipes-graphics/wayland/files ” 目录即可。原 NXP 论坛文档 patch 是基于 Weston 12.0.3 版本,这里对于 Yocto 环境配置的 12.0.4 版本做了一定的适配修改。 https://gitee.com/simonqin09/verdin-imx8mp-display-clone-mode/blob/master/0001-weston-imx-12.0.4-LF6.6.52_2.2.0-clone-mode-8MP.patch f). 最终完整 meta-customer-demos layer 文件结构如下 meta-customer-demos ├── conf │ └── layer.conf ├── recipes-graphics │ └── wayland │ ├── files │ │ └── 0001-weston-imx-12.0.4-LF6.6.52_2.2.0-clone-mode-8MP.patch │ └── weston_12.0.4.imx.bbappend g). 修改 bblayers.conf 和 local.conf 文件 ------------------------------- ### modify bblayer.conf ### --- a/build/conf/bblayers.conf +++ b/build/conf/bblayers.conf @@ -34,7 +34,7 @@ ${TOPDIR}/../layers/meta-openembedded/meta-python \ ${TOPDIR}/../layers/meta-freescale-distro \ ${TOPDIR}/../layers/meta-toradex-demos \ + ${TOPDIR}/../layers/meta- customer-demos \ \ \ ${TOPDIR}/../layers/meta-toradex-distro \ ### add below to local.conf ### # add Freescale EULA ACCEPT_FSL_EULA = "1" ------------------------------- h ). 编译 Yocto Linux image ------------------------------- # ## compile Reference-Multimedia image ### $ MACHINE="verdin- imx8mp " bitbake tdx-reference-multimedia-image ------------------------------- i ). Yocto Linux image 部署 参考 这里 通过 Toradex Easy installer 将上面编译好的 image 更新部署到模块 4 ). 修改部署方法之二:通过直接修改 Weston 源码 编译部署 a). 在不具备 Yocto 编译条件下可以考虑此方法。 b ). 参考如下下载对应版本 Weston-imx 源码,本文依然使用 12.0.4 版本示例,并进行修改 ------------------------------- ### download weston-imx source code ### $ git clone -b weston-imx-12.0.3 https://github.com/nxp-imx/weston-imx.git ### apply patch for clone mode ### $ cd weston-imx $ git apply ../../0001-weston-imx-12.0.4-LF6.6.52_2.2.0-clone-mode-8MP.patch ### modify meson.build file to adopt cross compile ### $ vi protocol/meson.build --- a/protocol/meson.build +++ b/protocol/meson.build @@ -1,5 +1,9 @@ dep_scanner = dependency('wayland-scanner', native: false) -prog_scanner = find_program(dep_scanner.get_variable(pkgconfig: 'wayland_scanner')) +if meson.is_cross_build() + prog_scanner = find_program('wayland-scanner', dep_scanner.get_variable(pkgconfig: 'wayland_scanner')) +else + prog_scanner = find_program(dep_scanner.get_variable(pkgconfig: 'wayland_scanner')) +endif dep_wp = dependency('wayland-protocols', version: '= 1.31', fallback: ) ------------------------------- c ). 参考如下文章编译并 export 交叉编译 toolchain 相关环境变量 https://developer.toradex.cn/linux-bsp/os-development/build-yocto/linux-sdks d ). 编译修改好的 weston-imx 源码 ------------------------------- ### export SDK environments ### $ source SDK_Install_Path/environment-setup-armv8a-tdx-linux ### compile ### $ cd weston-imx $ meson build/ --prefix=/usr -Ddoc=false -Dbackend-drm-screencast-vaapi=false -Dcolor-management-lcms=false -Dpipewire=false \ -Dbackend-x11=false -Drenderer-g2d=true -Dbackend-pipewire=false -Dbackend-rdp=false -Dbackend-vnc=false -Dxwayland=false $ DESTDIR=./opt/weston ninja -C build/ install ------------------------------- e ). 将编译好的 weston 相关库文件部署到 Verdin i.MX8MP BSP7.x Linux ------------------------------- ### package ### $ cd weston-imx/ build/opt/weston/ $ tar cjvf ../../../weston_mod.tar.bz2 * ### copy weston_mod.tar.bz2 package to Verdin i.MX8MP Linux ### ### deploy weston binaries ### root@verdin-imx8mp-06849028:~# tar xvf weston_mod.tar.bz2 / ------------------------------- 5 ). 多屏显示测试 a ). 上述修改部署完成后,不做任何修改, DSI-HDMI 和 native HDMI 屏幕默认启动后是 Extended 显示模式 b). 如下修改 /etc/xdg/weston/weston.ini 来使能 clone mode ------------------------------- --- a /etc/xdg/weston/weston.in i +++ b /etc/xdg/weston/weston.ini @@ -3,6 +3,7 @@ repaint-window=16 idle-time=0 #enable-overlay-view=1 +clone-mode=1 ------------------------------- c ). 重新启动后 DSI-HDMI 和 native HDMI 屏幕使能为 Clone 显示模式 d). 另外,如果是 DSI/native HDMI/native LVDS 同时显示的话,根据 NXP 论坛原文说明,可以在 /etc/xdg/weston/weston.ini 文件中增加如下配置组合,实现两个屏幕 Clone mode 显示,另外一个屏幕 Extented mode 显示。 ------------------------------- ... clone-connector-id= id_1 extend-connector-id= id_2 conn_id= id_3 mode= display_resolution ... ------------------------------- // 其中屏幕 connector-id 通过如下 modetest 命令可以获取 ------------------------------- ### get encoders devices ### # Type DSI - DSI # # Type TMDS - native HDMI # root@verdin-imx8mp-06849028:~# modetest -M imx-drm |grep -C 5 Encoders Encoders: id crtc type possible crtcs possible clones 37 33 DSI 0x00000001 0x00000001 39 36 TMDS 0x00000002 0x00000002 Connectors: ### get display connector-ids ### # connector-id 38 - DSI display # # connector-id 40 - native HDMI display # root@verdin-imx8mp-06849028:~# modetest -M imx-drm |grep -C 1 connected id encoder status name size (mm) modes encoders 38 37 connected HDMI-A-1 0x0 12 37 modes: -- value: 40 39 connected HDMI-A-2 0x0 20 39 modes: ------------------------------- 6 ). 总结 本文 基于 NXP i.MX8MP 处理器平台测试了 Yocto Linux 下多屏幕 Clone 模式显示,不过请注意如 NXP 论坛原文说明,此方法仅限于 NXP i.MX8MP 平台应用。 参考文档 https://community.nxp.com/t5/i-MX-Graphics-Knowledge-Base/Weston-clone-mode-on-i-MX8MPlus/ta-p/1791853

标签: arm

标签: arm