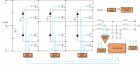

三电平逆变器是储能系统或者光储系统的基本工作拓扑,在这些应用中应用广泛,本文主要从基本工作原理及器件选型上进行讨论。 关控制在交流侧产生三电平相电压,经过滤波电路之后得到正弦波。 一 .NPC 和 ANPC 的拓扑概要分析 图 1 NPC 中性点箝位逆变器 上图 1 中描述了 NPC 的拓扑,这个是一个多电平拓扑,这个拓扑中所有开关都是额定电压设在一半的总线电压,器件的电压应力比较低,因此功率器件开关损耗也相对较低,所以在 NPC 拓扑中,对于 800V-1000V 的总线电压,可以使用 650V-700V 等级的器件,相比 1200V 器件可以达到更低的开关损耗。 NPC 拓扑的输出电流纹波较小,这会优化输出滤波电感的大小,用较小的电感维持相应的 THD, 拓扑不仅可以产生较小畸变的输出电压,同时可以最小化开关器件的 dv/dt 电压应力,从而减小 EMI. 这个拓扑提供了功率的双向传输,当开关频率高于 50kHz 时是更好的选择,因为其低的开关损耗和较高的效率。虽然控制上比较复杂,但是此拓扑改善了功率密度和效率等特性。作为一个双向 DC/AC 拓扑,它非常适合储能逆变器及光储系统中的逆变部分。 除了上述优势之外,其缺点也显而易见,比如开关器件较多,同时对应的门级驱动器也较多。由于使用了功率二极管,所以其热分布不均匀,热管理也是一个挑战。 图 2 ANPC 有源中性点箝位逆变器 相对于NPC拓扑而言,如上图 2 所示, ANPC 逆变器是一个 NPC 逆变器的改善版本, NPC 拓扑中的二极管在这个拓扑中变为了有源开关。这样的变化,使得系统可以得到更一致的损耗分布,使得热管理更容易,开关的导通电压可以减小,改善了效率和功率密度。 ANPC 拓扑的其余部分和 NPC 基本一致,后面我们会以 ANPC 拓扑为例,简述其基本工作原理。 二 .ANPC 三电平逆变器的基本工作原理 图 3 ANPC 的三相逆变器拓扑架构图 上述图 3 为 ANPC 三电平三相逆变器的拓扑架构简图,为了更进一步的简化分析,我们分离出单独的一相电路,如下图 4 所示。另外两相电路的运行原理类似,此处不详细分析。 图 4 ANPC 的单相逆变器桥臂 总体而言,每一相有 6 个开关器件,其中 Q1,Q5,Q2 在正半周期内为闭合状态, Q4,Q6,Q3 在电路负半周期为闭合状态。 Q2,Q3 为慢速开关,在每一个正弦半周期内,将电感连接到 Q1,Q5, 或者 Q4,Q6 的高频开关对,每一个快速开关对,在工作的半个周期内以同步降压模式运行。 图 5 ANPC 正半周期工作的状态分析 接下来,我们分析一下电路在正半周期内的工作情况。 其中,作为慢速开关,工作在 100Hz , Q2 在整个半周期内保持开启状态, Q1 主开关闭合时,电路处于激磁状态,建立从 V+ 总线电压到电感的电流路径。此状态下,由于 Q1 和 Q2 都打开,则 Q3,Q4 承受全部的总线电压,为避免器件之间不均匀,保持 Q6 开启, Q3 和 Q4 的中点连接到中性点,二者平均分配电压。 Q1, Q6 在正负半周期之间的死区时间内关闭,电感流过 Q5, Q2 续流 , 连续模式下, Q5 为同步二级管,电感器节点连接到中性点。在此状态下,续流时 Q3, Q4 只承受一半的总线电压,因此无需保持 Q6 接通实现电压平衡。 图 6 ANPC 负半周期工作的状态分析 负半周期工作情况如图 6 所示。类似于正半周期,在负半周期内工作时,作为慢管工作在 100Hz , Q3 一直保持开启。 在导通激磁阶段, Q3,Q4 导通,电感器连接到 V-,Q5 在该状态下开启,以便平衡 Q1,Q2 之间的电压应力。在主开关 Q4 关断续流状态下, Q6, Q3 维持电感电流,电感器开关节点连接到中性点。 以上就是 ANPC 的单独一相在整个周期的工作情况。 三. ANPC 拓扑的开关应力和损耗情况分析 根据上述原理分析,主功率器件只需要一半的总线电压的应力,所以 1000V 的直流总线电压下,可以使用 650V-700V 的功率器件。 其中由于拓扑运行需要, Q2 和 Q3 为慢速开关,运行在 100Hz 工频,所以可以选择普通的 Si 的功率 MOSFET 即可。而 Q1, Q5 及 Q4,Q6 都是运行于高频的功率器件,所以选择宽禁带器件,可以提升开关频率及功率密度。 除去平衡电压应力的开关管,同一时刻有两个开关器件导通(包含一个快管和一个慢管),所以对于导通损耗而言,需要根据相应允许的功耗去选择功率器件 Rdson 。 对于开关损耗而言, Q1,Q4 为控制的主开关对应于每一个半周期,因此会出现开关损耗。 Q5,Q6 为续流同步开关,因此会有零电压开关状态,在死区时间内体二极管导通,其存在正向压降和反向恢复损耗,而宽禁带器件的反向恢复损耗可以忽略。 Q2,Q3 的开关频率非常低,仅仅作为半周期的常通开关,所以其开关损耗可以忽略。 总结,以上简要分析 NPC 及 ANPC 拓扑的基本工作原理。 关注公众号“优特美尔商城”,获取更多电子元器件知识、电路讲解、型号资料、电子资讯,欢迎留言讨论。

标签: 拓扑

标签: 拓扑