作者:Karthik Gopal SmartDV Technologies亚洲区总经理 智权半导体科技(厦门)有限公司总经理 作为长期植根中国的全球领先的集成电路知识产权(IP)提供商,SmartDV一直在跟踪人工智能(AI)技术以及它对各个细分芯片领域的推动作用,同时也在不断地推出新的诸如IP、验证IP (VIP)和Chiplet这样的产品和服务,支持客户迅速开发AI SoC等新一代智能应用芯片去把握AI技术带来的新机遇。 AI技术在龙年岁末金龙摆尾实现了诸多突破,例如在CES 2025大展上许多行业组织和标准组织推出了新的协议和标准以满足AI应用的带宽需求;而DeepSeek把训练成本大幅下降之后,给更多的智能端侧设备带来了添加AI功能的动力,也为支持这些设备的AI SoC带来了春天。 SmartDV为智能时代已经做了前瞻布局和充分准备。在全球市场上,除了与主要的标准组织和行业联盟深度配合及时推出满足各种最新协议和规范的新产品,还参加了CHIPLET SUMMIT 2025和DVCON US 2025等重要行业活动,积极迎接智算时代的到来并支持客户们面向未来开展创新。 在中国市场上,SmartDV的努力在去年底于上海举办的“上海集成电路2024年度产业发展论坛暨中国集成电路设计业展览会(ICCAD 2024)”也得到了充分的展示。SmartDV中国团队为这个参加人数达到创纪录的7000人的大会带来了全方位的设计IP与验证IP(VIP)展示和精彩的演讲,致力于以定制化IP来帮助中国用户形成差异化优势,并加大力度与中国生态伙伴开展更深入的合作,推动集成电路设计产业在智能时代获得新的发展。 图片来源:ICCAD-Expo 中国半导体行业协会集成电路设计分会理事长魏少军教授在ICCAD 2024大会上的主题报告揭示,2024年中国集成电路设计产业全行业销售收入预计将达到6460亿元(约910亿美元),继续保持了两位数的增长,但是2024年的增幅低于WSTS预测的同年全球半导体产业总体营收增长率19%,为2004年来20年间首次发生。而随着各种具备AI功能的智能终端和智能汽车等应用在我国快速发展,正在带动了中国芯片设计产业链的创新,但是新的增长将更多得益于创新的发展模式。 图片来源:ICCAD-Expo SmartDV亚洲区总经理兼SmartDV在中国的独资企业智权半导体科技(厦门)有限公司总经理Karthik Gopal表示:“SmartDV长期看好中国集成电路设计产业的发展,并与许多中国芯片设计企业、IP开发商和设计中心(ICC)开展了多样化的合作;但是要继续保持高速发展,中国集成电路设计业需要抓住AI技术全面普及这个机会引入新的发展模式,例如基于定制IP的差异化芯片设计,以及企业间基于产业生态的合作。” 定制IP支持芯片设计企业创造产品差异化 SmartDV的代表分享了定制IP和产业生态合作加速中国芯片设计业发展的最新进展。他介绍到,SmartDV是一家全球领先的设计IP和验证IP供应商,目前可提供500多种IP产品,而且还可以根据客户的需求,为客户提供符合行业标准但又可以根据客户需求进行定制的IP产品,是业内少有的能够高速度、高可靠性和高成本效益地提供定制IP产品的供应商。 与其他厂商千篇一律的商业IP不同,定制IP可以为芯片设计企业的产品带来差异化的性能,甚至通过优化缩减芯片面积和降低成本,从而有助于避免因为同质竞争带来的价格战和低毛利。 SmartDV利用其独特的IP生成工具SmartComplier和数百位精通各种协议和标准的IP专家,可以快速生成符合客户特定产品定义的IP;与此同时,由于不需要研发人员参与IP生成过程,避免了引起人为错误的风险;此外,SmartDV还可以利用其业界最全面的验证IP组合之一,来对生成的IP进行反复验证,确保客户最终得到的是高质量的IP。 例如针对汽车智能化的需求,SmartDV 不久前宣布将其SDIO IP系列授权给RANiX,以集成到RANiX的车联网(V2X,Vehicle-to-Everything)产品中。SmartDV开发的SDIO IP提供功能强大的、高性能的数据传输能力,这对于V2X系统实现无缝功能集成至关重要。 SDIO接口支持处理器和存储器件之间的有效通信,并在存储之外集成和控制存储器运行,并同时连接外围设备,支持复杂系统所需的高性能和可靠性。这些IP内核推动了汽车组件之间的可靠通信,同时增强了诸如车辆安全通信、实时交通状况更新和驾驶员辅助功能等联网车辆技术。 面向智能化的机遇,大力推动基于产业生态的合作 除了展示和介绍自己的IP技术与产品,SmartDV还积极推动基于产业生态的合作,并与国内外合作伙伴们开展了许多交流与会谈,包括RISC-V IP提供商、大容量FPGA器件提供商、PHY IP提供商、硬件仿真及相关EDA工具提供商和集成电路设计中心等。SmartDV推动的这些合作已经初现成果,预示着将在2025年及今后很长一段时间内成为一种新的产业发展模式。 这种基于产业生态的合作通过与伙伴的产品进行预先集成和预先验证,以及联合市场推广活动和支持服务,不仅可以为包括客户及合作伙伴在内的各方带来产品更易集成和更快上市的新商业模式,还可以提供已验证的全面IP解决方案来提升价值和降低门槛,并且还能通过形成全芯片定制等竞争力更强的产品。 SmartDV推动的这种合作已经得到了行业伙伴的支持并受到客户的欢迎,例如在快速发展的RISC-V IP领域中,国内已有两家IP提供商与SmartDV达成了基于产业生态的合作关系。 展望2025 智能化时代已经到来,在经过20多年领域内的高速发展之后,中国集成电路设计产业将随着各种智能化技术的不断涌现和广泛应用,再次迎来新的发展机遇,同时也将形成中国集成电路设计产业独有的高速与高质量并进的发展模式. 为此,SmartDV将不仅为中国集成电路设计企业提供更多诸如面向AI SoC这类新芯片的高质量IP产品,而且还会通过定制化与许多国内企业开展基于产业生态的合作,全面支持用户通过打造更具竞争力的新一代芯片产品,实现产业的继续繁荣。

标签: Chiplet

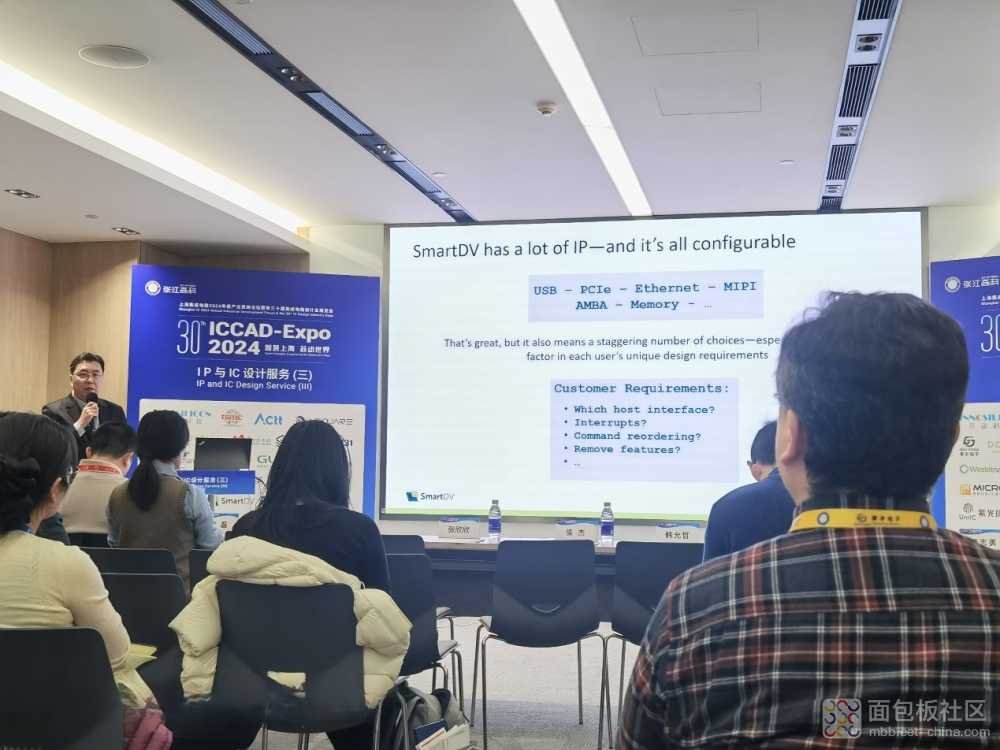

标签: Chiplet