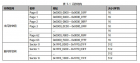

5. 嵌入式闪存( FLASH ) 5.1. 模块介绍 华大电子 MCU CIU32F011x3 、 CIU32F031x5 集成了嵌入式 FLASH 控制模块,该模块控制 FLASH 的擦除、编程以及读取数据。上电时会从 FLASH 中读取相关数据进行校验以及初始化配置,保证芯片程序在正确且安全的情况下运行。 5.2. 功能特点 • 支持高达 64K 主闪存空间的 FLASH • 存储器结构 – 主闪存空间 64K 字节 – 副闪存空间 4.5K 字节 • 指出对闪存空间的擦写、编程和读操作 • 支持对闪存空间访问限制和擦写保护 • 支持低功耗模式 5.3. 功能说明 5.3.1. 闪存结构 闪存空间由 32 位宽的存储单元组成,既可以存代码又可以存数据。主闪存块按 32 页(每页 1K 字节)分块,以页为单位设置写保护(参见存储保护相关内容) 注: 当主闪存空间 64KB 不够存放用户程序时,可把副闪存空间的扇区 0 至扇区 7 扩展为程序存放空间,即支持 68KB 的程序存放空间。 5.3.2. 闪存读保护 读操作在整个芯片工作电压范围内都可以完成,用于存放指令或者数据。当 NVR8 用户配置区经过自定义的保护配置后 ,SWD 连接时会对 FLASH 的代码数据执行保护机制。 注: FLASH 运行在 24MHz 工作频率,当系统时钟超过 30MHz 时,需要配置 TIMER_REG0 的 RC 参数,增加时钟周期数再把 FLASH 接口的数据写到寄存器。 5.3.3. 闪存擦除和烧写操作 烧写和擦除操作在整个芯片工作电压范围内都可以完成。烧写和擦除操作由下列 6 个寄存器完成,先根据烧写的时钟配置好烧写时序 (TIME_REG1) ,再配置烧写密码,配置好编程地址,最后配置好编程数据,即可开始执行烧写,然后等待操作结束。 烧写操作相关寄存器 • 时序寄存器 1 : TIME_REG1 • 密码寄存器 : NVR_PASSWORD/MAIN_PASSWORD • 编程地址寄存器: PROG_ADDR • 编程数据寄存器: PROG_DATA • 状态寄存器 : DONE 擦除操作相关寄存器: • 擦除控制寄存器: ERASE_CTRL 注: 需要注意的是, FLASH 在擦除 / 烧写的同时不可以从 FLASH 取数据,所以 FLASH 在擦除 / 烧写过程中会让总线停顿, 直到完成后才能继续运行。 沈阳芯硕科技有限公司是华大电子专业代理商,有技术问题可咨询芯虎论坛。

标签: 华大电子产品

标签: 华大电子产品