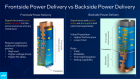

其实我们对 PowerVia 技术的解读,已经不是第一次了——前不久谈 2nm 工艺的文章才刚刚提过。这项技术之所以重要,从 Intel 的角度来看,在于它是 Intel 的半导体制造工艺于 2025 年“重回王座”的关键,而且是很关键。 最近 Intel 对 PowerVia 工艺做了更细节的内容分析,而且在 VLSI 研讨会上,还准备发布 PowerVia 技术的 paper 。 Intel 在市场宣传上,将 PowerVia 的重要性,抬到了与 2003 年 90nm 工艺应变硅, 2007 年 45nm 节点的 high-k 金属栅 (metal gate) ,以及 2012 年 22nm 节点的 FinFET 结构器件这三者相同重要的位置。 对半导体制造工艺熟悉的同学应该不会不知道上述三者对于 Intel 乃至行业的重要性,那么自然不会小觑 PowerVia 。另一个关键是, PowerVia 晶背供电技术,预计会在明年的 Arrow Lake 上应用——也就是传说中的 15 代酷睿处理器,虽然究竟是 14 代 refresh 还是 15 代,可能还不一定。 而以 PowerVia 为代表的这一类 Backside Power Delivery 晶背供电技术,台积电和三星也在搞。但如 2nm 工艺展望的文章里提到的,这两家要上同类技术的时间比 Intel 明显更晚。起码台积电已经确认,最早的 N2 工艺不会应用晶背供电——这项技术的采用起码要等到 2026 年的 N2P ,显然在时间线上就输了。 而这次 Intel 还专门公开了基于 PowerVia 技术的测试芯片 ( 名为 Blue Sky Creek ,复杂度还不低的一颗芯片 ) 的一些数据,就是急于向市场传达:东西我们已经做出来了,而且成熟度也很不错,大规模量产指日可待。这就给市场、客户和投资者树立了 Intel 在半导体制造工艺上的信心,则 2025 年“重回王座”的 flag 看着就很有希望了。 这样也就不难理解, PowerVia 现阶段对 Intel 的意义可能还不只是配合 Intel 20A 工艺,以及尽早用在 Arrow Lake 处理器上这么简单了。这篇文章,我们就来谈谈 Intel 的 PowerVia 技术,也算是 Backside Power Delivery 晶背供电网络的科普。 把一些东西移到晶圆背面 其实读过我们之前谈晶背技术文章的同学应该会知道, Backside Power Delivery 顾名思义是把某些供电轨移到了“背面”。与 Backside Power Delivery 相对的自然就是 Frontside Power Delivery 。 对逻辑芯片制造有了解的同学应该知道,一般芯片制造的过程,肯定是先搞定最底下那些很小的晶体管和器件 ——最下层一般都是最为精细的,我们所说某一代工艺节点最小的物理间距尺寸就在这里 ; 随后就开始往上“垒”,尤其晶体管上方是需要金属线互联、供电的。 Intel 10nm 工艺金属层间距,来源: Wikichip Fuse 不过这些金属层也不止一层那么简单,微观层面它们要连接大量晶体管和器件,宏观上则涵盖了处理器不同的组成部分 ; 另外电源布线自然也是其中的组成部分。当代的高性能处理器一般都会有 10-20 层的金属层。关注过我们此前解读 Intel 10nm/Intel 7 和 Intel 4 工艺文章的同学应该也很清楚,不同金属层 M0, M1, M2... 最小间距都有不同 ; 除了 M0, M1 之外,越往上层,间距越大。 Intel 4 工艺设计规则 比如 Intel 说, Intel 4 工艺节点逻辑部分要堆 16 层金属层,不同层的 pitch 间距从 30nm 到 280nm 不等。而再往上还有两个“巨大层” ( 上图中的 GM0/GM1) ,间距至少也是 1000nm+ ,用于电源布线,及布局外部连接。 这样一颗芯片是从最底下的晶体管,到最上层金属层。这就是典型的 Frontside Power Delivery ,供电与信号互联线路都在同一侧。这种方案有好有坏,好处后面谈。 其显著坏处就在于金属层更多,互联和供电都要走很远才能抵达晶体管,而且供电和信号两者间会有干扰,系统复杂性更高 ——设计和工艺技术要考虑的问题更多,也就影响到了面积利用。另外对于供电来说,更远的路径带来 IR 压降。以前这方面的问题还不大,但随着工艺节点迈进,器件间距越来越小,问题在整个系统中的占比增大,自然成为一个要被消除的关键点。 所有三星、台积电、 Intel 都将 Backside Power Delivery 加入到了半导体尖端制造工艺的技术体系里,也就是将供电连接的部分移到 wafer/die 的另一面,分离了供电和 I/O 。 Intel 的 PowerVia 就是这一思路的具体实施方案。 简单来说就是先把逻辑层、信号互联搞定,然后把 wafer 翻过来,在其上构建电源供电网络。当然其中肯定还涉及到另一面的打磨——起码要让供电能更近地接触到另一面的晶体管,在上面建起供电网络,也涵盖了 CMP(Chemical Mechanical Polishing) 清洁、光刻、蚀刻等等步骤。 用 PowerVia 技术先造一颗芯片 有关 PowerVia 的部分技术细节,我们放到后文去谈。首先还是来说说这个所谓的“晶背供电”究竟能给芯片、处理器带来多大的价值。先说说理论上的一些好处。首先是因为晶背供电的采用, M0 金属层的间距可以做得宽松些。 Intel 的数据是,原本 Intel 4 工艺的 M0 金属层间距为 30nm ,而在加上 PowerVia 以后,可以将间距放宽到 36nm 。换句话说,几乎是技术难度最高的这部分,其制造难度和成本都能有所放松。 然后就是前文提到的,供电路径长度变短了,自然降低了 IR 压降效应的影响 ; 在信号 I/O 另一侧,则显著降低了电源干扰的影响,提升了性能,有更大的余量去做设计优化。不过除了增加工序、存在技术难度之外,晶背供电也存在另外一些副作用——这个后面再说。 这次 Intel 是真正做了一颗 Intel 4 + PowerVia 的芯片,并将之与没有采用 PowerVia 、基于 Intel 4 工艺的芯片做对比的。首先还是要明确, PowerVia 实际上是为 Intel 20A 及后续工艺节点做准备的,所以很快要到来的 Meteor Lake( 传说中的 14 代酷睿 ) 并不会用上 PowerVia 。 而 Intel 之所以选择在 Intel 4 工艺上做实验,是基于此前我们谈到的 Intel 当前制造工艺步进的“ Tick-Tock ”方案,其中有一点是工艺的“模块化”。 Intel 为了降低复杂工艺技术迭代的风险,避免重蹈此前 10nm 时期的覆辙,对工艺技术的不同组成部分做了“解耦”。 比如说 Intel 20A 工艺,按照预期,这代工艺要采用 RibbonFET 结构的晶体管 ( 即 GAAFET) ,同时又要上 PowerVia 。这两个方向都有巨大的技术难度,所以将 RibbonFET 和 PowerVia 这两者解耦, PowerVia 在更早的节点上就做研发和制造的尝试,则 PowerVia 更多的是脱离于 RibbonFET 去做技术演进的。也就降低了节点迈进的风险。 这次 Intel 用 Intel 4 + PowerVia 造的这颗测试芯片名为 Blue Sky Creek 。这颗芯片之上有两片 die ,每片 die 上都有 Crestmont 核心——也就是 Meteor Lake 处理器的 E-core 部分。毕竟 Meteor Lake 本身就用 Intel 4 工艺造,“就近”测试 PowerVia 也合理。而且 E-core 是 Intel 异构 CPU 核心中,占地面积比较小的核心,测试芯片 4 个核心, die size 为 33.2mm ² (4mm x 8.3mm) ,也就不必搞得太过复杂。核心跑在 1.1V 3.3GHz 。 上面这张图是不用 PowerVia ,和用了 PowerVia 之后的单元尺寸,及包括 CPP 、 FP 、 M0 pitch 等在内的物理尺寸差异。关注 Intel 4 工艺的同学应当普遍都知道, Intel 4 节点只做了 HP 高性能单元库 ( 而没有做高密度等其他单元库,毕竟 Meteor Lake 是 chiplet 式的设计,部分 die 会让台积电负责制造 ) 。所以上图就是 HP 单元库。 加了 PowerVia 之后的单元,一方面是 M0 金属层间距变大了, fin pitch 和 contacted poly pitch 都没变。另一个比较大的变化是,单元 fin 的数量从 3 个减到 2 个,所以整个单元的尺寸就变小了,缩减幅度达到了 12.5% 。换句话说,这算得上是个 scaling booster 方案了,即晶体管间距变大的情况下,整体密度还增加了。 另外,没有用 PowerVia 的芯片,一侧是 15 层金属层 +RDL 层 ; 而用了 PowerVia 之后,一侧信号 I/O 变为 14 层,另一侧是 4 层 +RDL 层。两侧加起来,层数是增多了的。但其中 4 层在另一侧,也就是所谓的“背面” (backside) ,本身在复杂性上就不需要那么瞻前顾后了。加上 M0 间距还变大了,换取多出来的几层金属层也是值得的。 虽然 Intel 没有给具体的密度数字,不过上面这张图展示了所谓的“ cell utilization ”单元占地面积利用率,在某一点能够到 95% 。 从更直观的电性能角度来看,前文提到了 PowerVia 能减少 IR 压降。 Intel 的数据如上图所示,测试芯片测得的 IR 压降能低 30% 。如此一来能效就提高了,因为在这个过程里能量损失变小了。相对的 Crestmont 核心最高频率能提升 6% ——这就是实打实的 CPU 性能红利了。 另外据说测试发现,测试芯片上几颗 Crestmont 核心的压降数字情况不同,而 Frontside Power Delivery 的常规 Intel 4 工艺就没有这种情况。或许这对 DIY 发烧友、超频爱好者而言又是个好事,因为这表明未来基于 PowerVia 制造的芯片,某些核心会有更好的“体质”。 很多人真正关心的数据是, PowerVia 的良率情况怎么样了,毕竟隔壁两家的晶背供电技术都还没影。 Intel 给的数字是这次实验性质的 Intel 4 + PowerVia ,比传统 Intel 4 差“ 2 个季度 (2 quarters) ”。这个值具体说的应该是不良率 (defect density) 。 虽然我们对 “ 2 个季度”没啥概念,但听 Intel 的意思是基本上和非 PowerVia 版的 Intel 4 差不多。可靠性和晶体管电特性也达到了量产的预期。至少在测试芯片上没有发现供电相关的可靠性问题。 晶背供电的固有问题,和 Intel 的解决方案 接下来该谈谈 Backside Power Delivery 产生的一些固有问题了。最大的问题当然是制造工序增加、难度增大——这是先期显而易见的、可预期的,也就是如何达成量产 ; 其次是可靠性问题——就 Intel 的数据来看,这两个问题解决得还不错。 真正的问题在于散热和 debug 问题怎么解决。对于传统方案,也就是 Frontside Power Delivery 而言,从底层晶体管开始构建,然后 MOL 再加上面一堆金属层—— die 自底层往上层搞完以后,像 Intel 的 CPU 封装要用倒装方案 (flip chip) ,也就是封装的时候 die 要翻个面,倒扣到封装基板上。此时,晶体管在上,金属层在下。 晶体管在上,对于散热和 debug 都有好处。因为晶体管在上,这一面也就与封装的散热介质离得更近,主要热源就能被及时降温 ; 而对 debug 来说,一般的 debug 工具显然也更容易访问晶体管。 那么当 PowerVia 技术在 wafer/die 的另一侧装上了供电线路,显然就将晶体管层夹在了中间。这对散热和 debug 都是不利的。其实 Intel 没有针对这两个问题,谈太多他们是怎么解决的,或者采用了哪些缓解方案。但他们给了热与 debug 的测试数据。 给定不同功耗,对应温度曲线,不用 PowerVia 和用了 PowerVia 方案是差不多的。而且据 Intel 所说测试是特意做了热负载加强的,以期在更高热密度时,温度也不会爆表。 Intel 说他们找到了在晶背供电结构下的散热缓解策略,达成与传统普通单面供电相似的水平。 Debug 的问题, Intel 说开发了一套新的 debug 技术,来解决新结构的问题。 Intel 表示在造这颗测试芯片的时候,特意埋了一些错误在其中,不让验证团队知道。而验证团队最终基于新的方案,找到了所有的 bug 。“我们在过去这些年,就发展 debug 能力方面取得了巨大的进展,并且在 Blue Sky Creek 之上得到了证明。” 最后来看两个 Intel 特别提到的,独属于 PowerVia 的技术点。其一是前文提到,在实施 PowerVia 方案的时候,要对 wafer 背面进行“打磨”,令其薄到将近可以接触晶体管的程度。这么做是会让 wafer 的刚性大打折扣的。所以在正面都搞完之后, Intel 在 wafer 正面键合了一片载体晶圆 (carrier wafer) ,来承载背面的制造过程。 到制造完成之后,这片 carrier wafer 也仍旧作为芯片的一部分存在了,当然在真正收工之前,这片后装的 wafer 也是需要打磨到对应薄度的。从直觉来看,这么做似乎又将加重散热问题,毕竟这是又多留了一层没什么价值的东西在芯片上。 另外一个技术点是 Nano TSV ,即用 TSV 来实现供电布线。如上图所示,最右侧的是 Intel 的 PowerVia 方案,另一侧的电源轨直接接 Nano TSV( 纳米级别的 TSV 硅过孔 ); 相比于业界的 Buried Power Rail 方案,供电明显更直接——似乎在设计和制造上,也避免了这部分电源轨布线 (routing) 的复杂度。这一点应该也是 PowerVia 叫做 PowerVia 的原因 ... 如 Intel 此前的路线图标识,明年的 Arrow Lake 处理器上就能见到 PowerVia 的身影,虽然其实就用户层面也不会有什么感知。但如文首所述, PowerVia 是否如约而至,以及和 Intel 20A 的 RibbonFET 共同发挥多大作用,会成为 2025 年 Intel 能否找回半导体制造王者地位的关键。至少就目前 Intel 公开的这些信息来看,希望好像真的就在不远处了。 关注公众号“优特美尔商城”,获取更多电子元器件知识、电路讲解、型号资料、电子资讯,欢迎留言讨论。

标签: PowerVia技术

标签: PowerVia技术