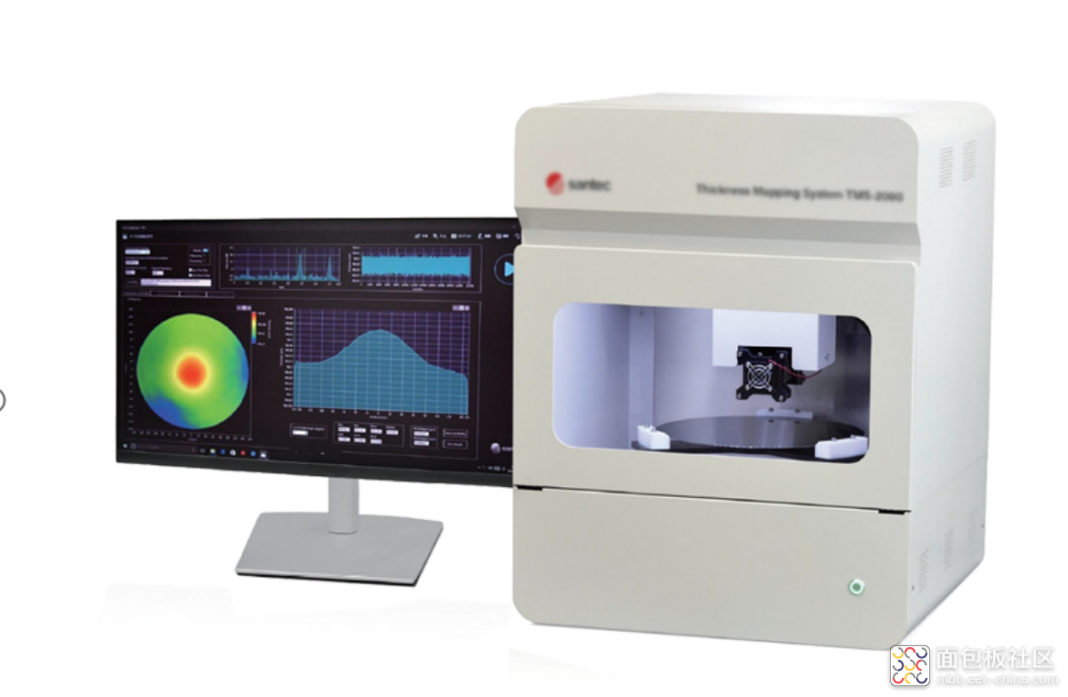

摘要:碳化硅衬底切割对起始位置精度与厚度均匀性要求极高,自动对刀技术作为关键技术手段,能够有效提升切割起始位置精度,进而优化厚度均匀性。本文深入探讨自动对刀技术的作用机制、实现方式及其对切割工艺优化的重要意义。 一、引言 碳化硅衬底是第三代半导体器件的核心基础材料,其切割质量直接影响器件性能与成品率。在碳化硅衬底切割过程中,起始位置精度不足会导致切割路径偏移,造成材料浪费与加工误差;而厚度不均匀则会影响后续芯片制造工艺的稳定性。自动对刀技术通过精确确定刀具与工件的相对位置,为提升切割起始位置精度与优化厚度均匀性提供了有效途径。 二、自动对刀技术原理与分类 (一)技术原理 自动对刀技术基于传感器获取刀具与工件表面的位置信息,通过数据处理与控制系统实现刀具位置的精确调整。其核心在于快速、准确地感知刀具与工件的接触状态,将物理接触信号转化为电信号或数字信号,进而驱动执行机构完成对刀操作 。 (二)常见分类 常见的自动对刀技术包括接触式对刀与非接触式对刀。接触式对刀通过刀具与工件直接接触,利用压力传感器、电感传感器等检测接触瞬间,实现位置校准;非接触式对刀则借助激光、红外等光学手段,在不接触工件的情况下测量刀具与工件的相对位置,具有对刀具和工件无损伤、测量速度快等优势。 三、自动对刀技术对切割起始位置精度的提升 (一)消除系统误差 机床在长期使用过程中会产生机械磨损、热变形等系统误差,影响切割起始位置精度。自动对刀技术能够实时检测刀具位置,通过补偿算法修正机床坐标系与工件坐标系之间的偏差,消除因机床误差导致的起始位置偏移,确保刀具准确落于预设切割起始点。 (二)提高重复定位精度 对于批量碳化硅衬底切割,自动对刀技术可在每次切割前自动校准刀具位置,避免人工对刀的主观性与误差,显著提高切割起始位置的重复定位精度。即使在长时间连续加工过程中,也能保证每片衬底的切割起始位置一致性,为后续切割质量稳定奠定基础。 四、基于起始位置精度提升的厚度均匀性优化 (一)保证切割路径准确性 精确的起始位置确保了切割路径严格按照预设轨迹进行。在碳化硅衬底切割中,若起始位置存在偏差,切割过程中刀具受力不均,易导致切割深度变化,进而造成厚度不均匀。自动对刀技术使刀具从准确位置开始切割,保证切割过程中各点切削深度一致,有效提升厚度均匀性。 (二)实时反馈与调整 自动对刀系统可与切割过程监测系统联动,在切割过程中实时监测刀具位置与切割参数。一旦检测到厚度异常趋势,系统能够快速反馈并调整刀具位置或切割参数,及时纠正偏差,维持切割厚度的稳定性,实现对厚度均匀性的动态优化。 五、自动对刀技术的实现与应用 (一)硬件系统搭建 自动对刀技术的实现依赖于高精度传感器、高性能控制器与稳定的执行机构。选用分辨率高、响应速度快的传感器(如纳米级精度激光位移传感器)实时采集位置信息;采用运算能力强的控制器进行数据处理与算法执行;搭配高精度伺服电机等执行机构,确保刀具位置调整的准确性与快速性。 (二)软件算法优化 开发专用的自动对刀软件算法,实现传感器信号的滤波、处理与分析,以及对刀策略的智能化决策。结合机器学习算法,根据历史对刀数据与切割结果,优化对刀参数与补偿算法,提高自动对刀的精度与适应性,使其更好地满足碳化硅衬底切割工艺需求。 高通量晶圆测厚系统运用第三代扫频OCT技术,精准攻克晶圆/晶片厚度TTV重复精度不稳定难题,重复精度达3nm以下。针对行业厚度测量结果不一致的痛点,经不同时段测量验证,保障再现精度可靠。 我们的数据和WAFERSIGHT2的数据测量对比,进一步验证了真值的再现性: (以上为新启航实测样品数据结果) 该系统基于第三代可调谐扫频激光技术,相较传统双探头对射扫描,可一次完成所有平面度及厚度参数测量。其创新扫描原理极大提升材料兼容性,从轻掺到重掺P型硅,到碳化硅、蓝宝石、玻璃等多种晶圆材料均适用: 对重掺型硅,可精准探测强吸收晶圆前后表面; 点扫描第三代扫频激光技术,有效抵御光谱串扰,胜任粗糙晶圆表面测量; 通过偏振效应补偿,增强低反射碳化硅、铌酸锂晶圆测量信噪比; (以上为新启航实测样品数据结果) 支持绝缘体上硅和MEMS多层结构测量,覆盖μm级到数百μm级厚度范围,还可测量薄至4μm、精度达1nm的薄膜。 (以上为新启航实测样品数据结果) 此外,可调谐扫频激光具备出色的“温漂”处理能力,在极端环境中抗干扰性强,显著提升重复测量稳定性。 (以上为新启航实测样品数据结果) 系统采用第三代高速扫频可调谐激光器,摆脱传统SLD光源对“主动式减震平台”的依赖,凭借卓越抗干扰性实现小型化设计,还能与EFEM系统集成,满足产线自动化测量需求。运动控制灵活,适配2-12英寸方片和圆片测量。

标签: 晶圆厚度

标签: 晶圆厚度