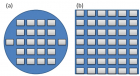

多家公司正在开发或增加面板级扇出封装,以降低高级封装的成本。 晶圆级扇出是几种高级封装类型之一,该封装可以在IC 封装中集成管芯,MEMS和无源器件。这种方法已经投入生产多年,并且以200mm或300mm晶圆尺寸的圆形晶圆形式生产。 大块方形面板上的扇出式封装要困难得多,而且预计不会很快被大量采用。尽管如此,所有高级封装的问题之一仍然是成本,而ASE,Powertech,Nepes和Samsung等公司正在寻求面板级封装以提供规模经济。面板比圆形晶圆处理更多的封装,从而降低了成本。例如,根据ASE的数据,一个300mm的晶圆可以处理2,500个6mm x 6mm的封装,而600mm x 600mm的面板可以容纳12,000个封装。 图1.具有(a)晶片形式和(b)面板形式的扇出包装。资料来源:日月光 图2. PLFO设备的封装轮廓,其中(a)为顶视图,(b)为横截面图。资料来源:ASE。 尽管如此,经过多年的努力,面板级扇出仍然具有挑战性。迄今为止,Powertech和三星是限量生产的唯一供应商。大多数人仍在开发或探索该技术,而其他人则不予考虑。 标准是这里的绊脚石。几家公司正在使用不同的面板尺寸来开发该技术。这使得某些设备制造商难以投资和制造用于该技术的系统。另外,面板扇出需要大量以保持线路正常运行。如今,几乎没有什么大批量产品可以填满整个面板级生产线。 TechSearch International总裁Jan Vardaman在最近举行的国际晶圆级封装会议(IWLPC)上说:“除非拥有高水平的参赛者,否则您将无法进行座谈。” “您绝对需要大批量的产品,否则您将无法做,因为您无法填补界限。” 通常,采用传统晶圆格式时,扇出封装供应商总共具有足够的容量来满足目前的需求。由于这个和其他原因,面板扇出被大量采用。瓦尔达曼说,曾一度计划在2019年实现量产。“也许在明年年底。” “它可能更像是2021年或2022年时间范围内能解决的。” 但是,在扇出封装这一领域还是有不少行动。主要进展包括: 三星的半导体部门最近从另一个分支机构三星电子机械(SEMCO)那里收购了面板级扇出装置。 Nepes最近从Deca收购了扇出生产线。Nepes还获得了Deca的晶圆级和面板级扇出技术的许可。 日月光着眼于开发使用面板的高密度扇出。 来自欧洲的一个小组正在开发面板上的能量收集装置。 面板挑战 传统上,IC供应商依靠芯片扩展来提高其设备。在缩放方面,其想法是在每个处理节点的单片芯片上封装更多的晶体管,从而以更低的每个晶体管成本实现更快的芯片。 芯片扩展并没有消失,但是在每个节点上它变得越来越困难和昂贵,促使许多IC供应商寻找替代方案。获得扩展优势的另一种方法是将多个不同的芯片放入高级封装中,这也称为异构集成。 先进的封装已经存在多年了。但是今天桌上有许多新的高级封装选项。当前提供软件包或解决方案一部分的公司正在评估新的和不同的选择。 联电公司市场营销副总裁史蒂文·刘说:“高级封装将在后摩尔定律时代变得更加重要。” “ UMC和其他公司在2.5D中介层市场中起着关键作用,该市场已被全球领先的客户采用并在批量生产中发挥了作用。尽管UMC不提供扇出封装解决方案,但我们将继续研究其他新的高级封装方法,或与OSAT合作伙伴合作。” 在封装市场的高端,该行业使用2.5D技术。在2.5D,管芯被堆叠或并排放置由端上的顶部插入器,其包含通过硅通孔(TSV)的。中介层充当芯片和电路板之间的桥梁。 同时,在扇出封装中,管芯被封装在晶片上,通常称为晶片级封装(WLP)。在扇出的一个示例中,DRAM裸片堆叠在封装中逻辑芯片的顶部。 ASE的工程部高级主管John Hunt说:“您不必将其限制为具有扇出功能的单个芯片。” “您既可以进行异构集成,也可以进行同质集成,您可以在其中拆分裸片并将其组合成扇形封装。您可以利用扇出的电气连接优势来互连不同的管芯。” Amkor,ASE,JCET,TSMC和其他公司出售基于传统晶圆级格式的扇出封装。苹果,英飞凌,恩智浦,高通和其他公司正在使用扇出套件。 扇出非常适合汽车,服务器,智能手机和其他系统。Veeco光刻技术市场营销高级总监Shankar Muthukrishnan表示:“一般来说,供热产品已经开始流行。“越来越多的OSAT和IDM开始开始批量生产,我们预计这一趋势将继续下去。” 并非所有芯片都需要扇出。实际上,当今的芯片中有很大一部分都采用更传统,更便宜的封装类型。 成本是扇出的最大障碍之一。为了更广泛地采用扇出,该行业将继续降低该技术的成本。降低成本的另一种方法是转向面板级生产工艺。 但是,面板级处理具有挑战性。供应商正在使用各种面板尺寸来开发该技术,例如510mm x 415mm,510mm x 515mm,600mm x 600mm等。 缺乏标准对设备行业来说是个问题。一些设备供应商已经为某些(但不是全部)面板尺寸开发了工具。还有一些人在观望,直到出现标准尺寸并开始起飞。 作为回应,SEMI正在制定面板尺寸标准。该贸易组已将面板选项的范围缩小到510mm x 515mm和600mm x 600mm两种尺寸。 无论如何,行业都需要一个标准。“我们必须就统一的面板尺寸达成共识,” AT&S的应用工程师Joseph Dang在IWLPC的面板讨论中表示。“这会影响我们在其上制造这些基板的设备。它会影响化学镀铜和光刻工具。所有这些都需要特定的设备来处理特定的面板尺寸。它们不能灵活地处理各种尺寸。这会造成混乱的环境,我们有六,七或八家基板尺寸不同的基板供应商。” 经济学也起着作用。建造面板级生产线的成本约为1亿至2亿美元。但是公司必须有足够的数量来确保回报。否则,这是赔钱的主张。 在面板上批量生产没有意义。但是,对于大容量设备,面板更具意义。“仍然有很多挑战。哪里可以找到这种技术的高容量?”问椿乡李,首席技术官JCET。 生产中的第一个面板扇出封装涉及低密度产品,而不是高端封装。低利润产品很难获得可观的回报。 如果这还不够的话,面板扇出与晶圆级扇出同样面临许多制造挑战。通常,在晶圆扇出流程中,晶圆是在fab中进行处理的。将晶片上的芯片切成小块,并放置在晶片状结构中,并在其中填充环氧树脂模塑料。这称为再生晶片。 然后,在化合物内形成重新分布层(RDL)。RDL是铜金属连接线或走线,可将封装的一部分电连接到另一部分。RDL用线和间距测量,线和间距是指金属走线的宽度和间距。 在晶圆扇出封装中,主流的RDL技术是5-5μm线/间距及以上,但有些正在开发1-1μm及以下的领先封装。 扇出并不是一个简单的过程。在流动期间,晶片状结构易于翘曲。然后,当将裸片嵌入晶片中时,它们趋于移动,从而引起称为裸片移位的不良影响。这影响产量。 通常,面板扇出遵循相似的制造流程。当然,区别在于模具是在面板中处理的。但是,与晶圆扇出一样,面板也容易翘曲。模具转移是一些RDL挑战的问题。 尽管如此,业界已经证明它可以制造具有较小侵蚀性RDL(5μm-5μm及以上)的面板扇出封装。这涉及容纳更简单的ASIC和电源管理IC(PMIC)的封装。 最终,业界希望生产2μm-2μm及以下的面板扇出封装。这涉及具有复杂ASIC,处理器和内存立方体的高密度封装。 “我们正在谈论要在实际的封装中增加至少两到三倍的模具。2μm-2μm将在更小的空间内为您提供更多,” Onto Innovation应用工程总监Keith Best说。Nantos和Rudolph合并后,Onto于最近成立。 要使面板扇出在2μm-2μm之间,说起来容易做起来难。“首先,面板尺寸的标准化尚未浮出水面,” Brewer Science WLP材料技术总监Kim Yess说。“对于面板而言,由于基板的翘曲以及用于图案化的工具和材料的能力,低于2μm的线/间距变得非常具有挑战性。我不确定≤2μm的互连对于面板工艺是否真正有意义,因为它们能够制造出比市场/客户要求更多的设备。此外,这种方法从一开始就不会像使用标准的300mm设备和方法那样具有成本效益。” 在面板处理流程中,使用各种设备有几个关键步骤。例如,光刻是对RDL和封装的其他部分进行构图的关键技术。在晶圆级扇出中,这些工具能够在2µm-2µm及以下的尺寸上对RDL进行构图。 光刻工具也可用于面板扇出,但挑战有所不同。Veeco的Muthukrishnan说:“请记住,面板越大,对产量和翘曲的影响越大,而翘曲会影响生产率和成本。” 模具在面板扇出中的移动将影响可达到的分辨率。实现2-2µm的分辨率将是一项挑战,而且成本可能超出预期。小组将来有可能实现这一目标,但可能涉及其他步骤或增加了工艺成本。” 除光刻外,面板扇出还需要其他类型的设备。KLA ICOS部门总经理Pieter Vandewalle表示:“在过去的一年中,我们在采用面板扇出封装方面取得了显着进展,更多的参与者开始了试生产,并且一些参与者已经进行了批量生产。” “虽然2-2µm及以下的样品已经在研发中,但我们认为要在面板的大批量生产中看到这一点还需要几年的时间。大多数处理工具都可用。但是,主要挑战似乎在于实现高产量。” 检查和计量也是流程的关键部分。检测工具在晶圆或封装上寻找缺陷,而计量系统则对结构进行了表征。 Vandewalle说:“ 2-2µm的检查和计量已经可以用于晶圆级处理。” “面板级2D和3D检测和计量工具可用于小批量制造,并将在推动采用面板扇出方面发挥关键作用。” 专家组可能需要不同的检查/计量技术。例如,CyberOptics销售基于相移轮廓仪技术的计量单元。它识别并拒绝由发亮的部件和类似镜子的表面引起的多次反射。 CyberOptics总裁兼首席执行官Subodh Kulkarni表示:“从我们的角度来看,我们正在检查晶圆还是面板都不会改变任何东西。” “面板检查客户似乎更喜欢具有较大视野的技术来更快地覆盖整个面板。” 谁在做什么? 如今,大约有六家公司致力于面板扇出,而其他公司则有不同的策略。例如,英特尔一直在开发用于封装而非扇出的面板级工艺。台积电还没有计划开发面板扇出技术,称晶圆扇出可以满足所有要求。 其他人正在追求它。例如,去年,SEMCO推出了业界首个面板扇出套件。该软件包集成在三星的Galaxy智能手表中,将应用处理器与PMIC结合在一起。它具有三层RDL,厚度为7μm-8μm。 在最近收购SEMCO的面板部门之后,三星正在推动这项技术的发展。“我们正在计划可穿戴设备的下一个产品。基本任务是在有限的尺寸范围内实现更多功能。”三星电子的Junghwa Kim在IWLPC的论文中说。 为了减少面板扇出时的封装尺寸,三星正在探索将两个芯片彼此叠置的想法。 同时,一段时间以来,日月光一直在开发使用600mm x 600mm格式的面板扇出。在面板方面,日月光希望在明年内投入生产。ASE的Hunt说:“我们将把面板用于低密度产品和高密度2μm以及更少的空间和空间产品。” “这是用于网络应用程序和新的AI。AI需要更多的计算能力和内存。” 如今,ASE正在根据自己的技术交付晶圆级扇出封装。它还基于一家名为Deca的技术生产M系列晶圆扇出线。Deca开发了一种技术,可以计算和补偿生产流程中的模头偏移。 对于面板扇出,ASE计划将Deca的M系列以及专有的高密度扇出封装(称为衬底上扇出芯片(FoCoS))投入生产。 ASE正在开发一种具有高带宽存储器(HBM)的FoCoS扇出技术版本。HBM面向高端系统,将DRAM裸片彼此叠放,并通过叠层与TSV进行连接,从而实现更多的I / O和带宽。 通常,HBM集成在更昂贵的2.5D封装中。“问题是成本相对较高。中介层的采购具有挑战性,”亨特说。 FoCoS不需要插入器,使其比2.5D便宜。最大的FoCoS封装可包含约9个管芯,因此封装相对较大。他说:“我们可以在300mm的晶片上放置10至12个封装,这在生产上并不经济。” ASE希望将面板用于这些大封装类型以降低成本。他补充说:“我们希望使用600mm面板,因为这些封装可能会变得很大。” 同时,Nepes一直在开发使用600mm x 600mm格式的专有面板扇出技术。 最重要的是,Nepes最近收购了Deca在菲律宾的晶圆级封装生产线。Nepes还获得了Deca技术的许可。 最终,Nepes将基于Deca的技术生产晶圆级和面板级封装。因此,该行业现在拥有Deca技术的两个来源-ASE和Nepes。 同时,Powertech至少在限量生产中正在出货面板扇出产品。然后,包括ASM Pacific,陶氏,华为,铟,JCAP和Unimicron在内的一个小组正在开发它。 值得一提的是,一个名为smart-MEMPHIS的欧洲项目正在使用面板扇出技术开发压电MEMS采集设备。该器件集成了一个基于MEMS的能量收集器,一个ASIC和一个超级电容器。应用包括用于健康监测的起搏器和无线传感器网络。 面板扇出是此处的关键推动因素。“这项技术非常适合诸如目标能量收集器之类的应用,在这些应用中,异构组件必须集成到小型化系统中,” smart-MEMPHIS项目的一部分,弗劳恩霍夫(Fraunhofer)副组长Tanja Braun说。 结论 显然,面板扇出为客户提供了一些新选择。但是,这项技术还需要时间。 它还将需要更多的投资。一些财大气粗的供应商将实现这一目标。但是投资回报率是不确定的。结果,随着时间的流逝,有些人可能会丢掉毛巾。 本文译自: Semiconductor Engineering ,原文链接:semiengineering.com/planning-for-panel-level-fan-out

标签: 面板级扇出型封装

标签: 面板级扇出型封装