testbench的实现方法多样,而且还不断涌现出新方法,这些都是人们在为更好的验证设计做的努力。如

VHDL,verilog,systemC,systemverilog均可以,但是真正的实际应用中绝对不是单独应用,而是将他们结合起来,使你的验证更方便,更全面。

由于系统验证的庞大,我们还是从最简单的,最熟悉的上手,就先单独用VHDL语言来写仿真语言,当然VHDL语言我们已经比较熟悉了,但是有个比较大的区别是,我们以前都是尽量学习能够综合的语言,但是在仿真中经常会用到一些行为级描述的语言,他们是不能被综合成逻辑的,但是却绝对可以让我们的验证更加高效方便,但是我们也不单独来讨论VHDL中哪些语言是能够综合,哪些语言是不能综合的,重点将会放在testbench的一般结构,编写testbench的一般思想,以及更多的是实际接触,以实际的例子与前面的可综合逻辑相结合达到完整的系统设计的上的!

testbench的几种思路:

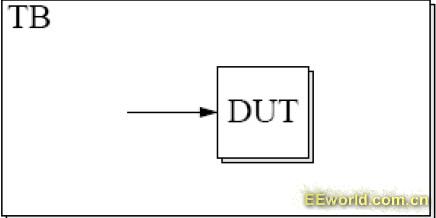

一、只在testbench中实例化DUT(design under test),激励输入是在testbench中临时产生的,只能用于简单逻辑。优点:简单,易操作。缺点:复用性差 ,效率低 模型如图1所示

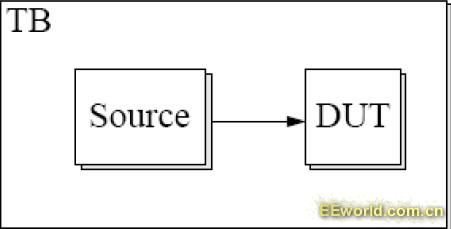

二、DUT的输入由单独的一个文件产生,在testbench中实例化两上entity,可以复杂输入,简单输出的模块。模型如图2所示

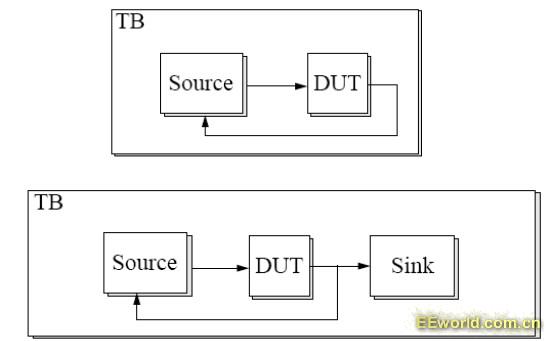

四、可以根据仿真输出来修改输入激励的,可以自动通过输出来修改输入,使验证更加准确。如图4所示的模型

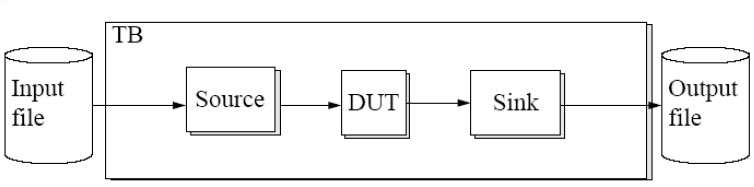

五、有文件做为testbench的输入,输出的模型。仿真中需要顺序的输入大量数据,以及接收相应的数据,可以通过从文件中读入数据,然后将产生的数据存入文件,使复杂系统验证更加方便。模型如图5所示。

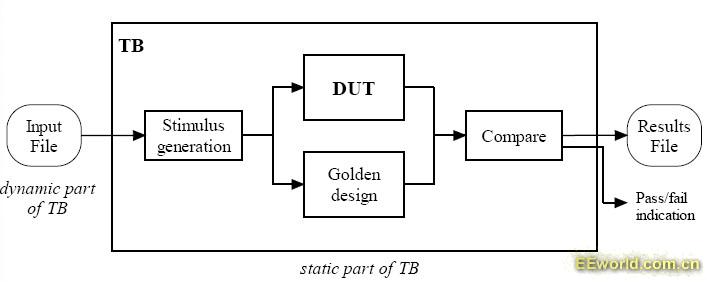

六、可以将激励同时输入自己设计的模块和已经验证了相同模块,比较二者输出。模型如图6所示。

图1

图2

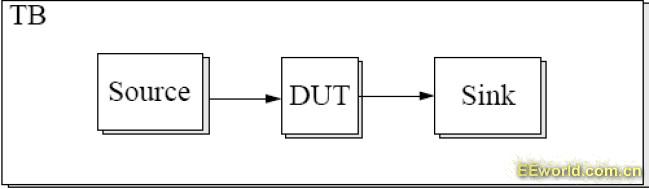

图3

图4

图5

图6

本文来源于:电子工程世界

/2

/2

文章评论(0条评论)

登录后参与讨论