VHDL的循环语句有三种:for循环、while循环和无限循环loop end loop,实际上,1oop…end loop可以看作是循环条件永远为真的while循环。在行为综合中,循环语句的处理是极其复杂的。

在寄存器级进行综合,要求for循环的上下界必须是静态已知,否则是不可综合的。VHDL定义了next和exit语句来中断循环的正常执行,现在的综合工具都可以处理这两种语言结构。

注意:FOR ...GENERATE 和FOR...LOOP的语句不同,在FOR ...GENERATE语句中所列举的是并行处理语句。因此,内部语句不是按书写顺序执行的,而是并行执行的,这样的语句中就不能使用EXIT语句和NEXT语句。

通过综合下面这段代码来了解FOR...LOOP的可综合性:

entity loop_syn

is

port (

sel

: in std_logic_vector(1 downto

0);

din

: in std_logic_vector(15 downto

0);

dout

: out std_logic_vector(3 downto 0);

din1

: in std_logic_vector(15 downto

0);

dout1 : out std_logic_vector(3 downto

0));

end

loop_syn;

architecture synlogic of loop_syn

is

begin -- synlogic

loop1 : process (din, sel)

begin -- process

loop1

for i in 0 to 3 loop

dout <= din((i+1)*4 - 1 downto

i*4);

exit when sel = i;

end loop;

-- i

end process loop1;

case1 : process (din1, sel)

begin -- process

case1

case (sel) is

when "00" =>

dout1 <= din1(3 downto

0);

when "01" =>

dout1 <= din1(7 downto

4);

when "10" =>

dout1 <= din1(11 downto

8);

when "11" =>

dout1 <= din1(15 downto

12);

when others =>

dout1 <= (others =>

'0');

end case;

end process case1;

end

synlogic;

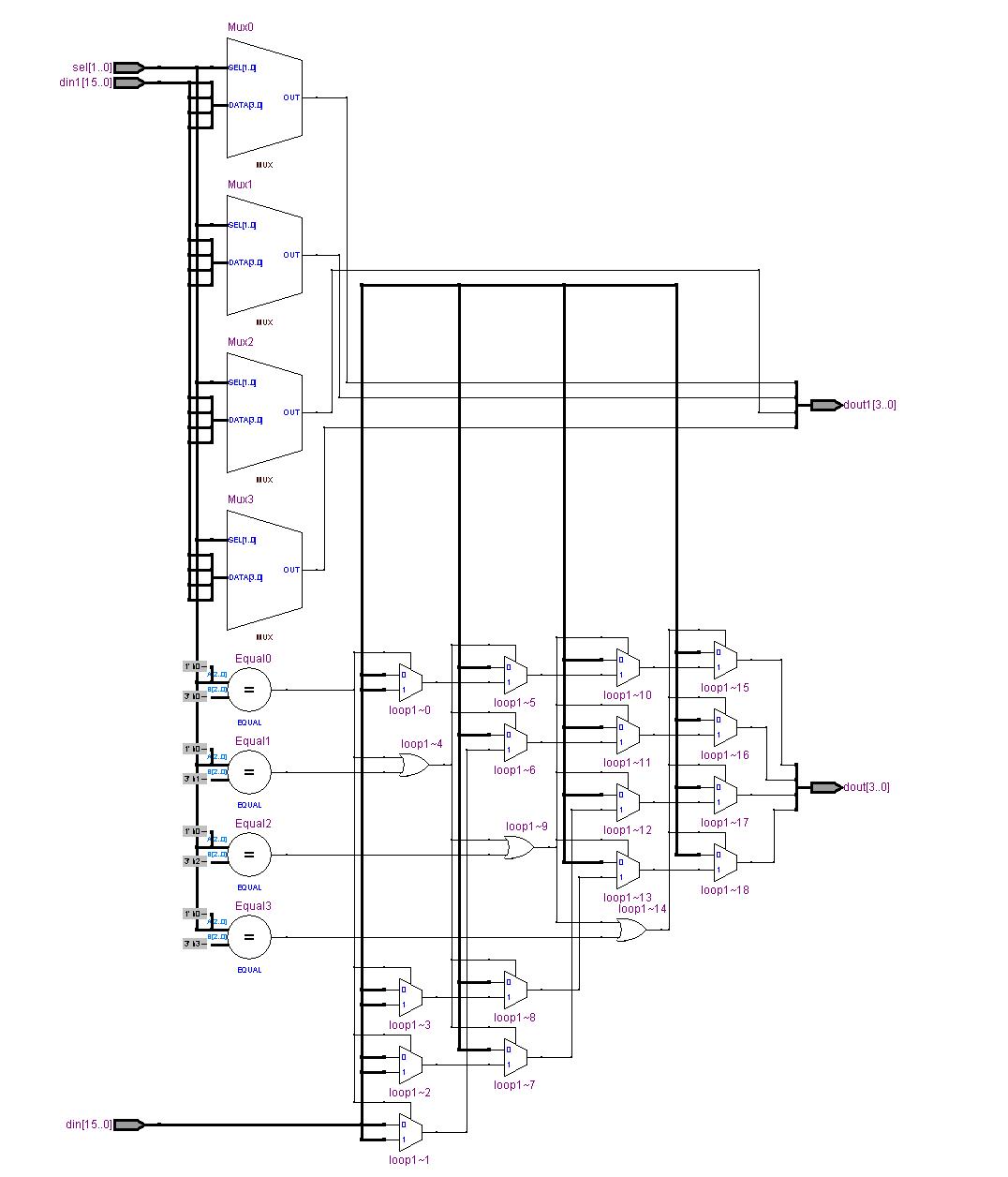

case1和loop1用两种不同的风格描述了两种相同功能,首先我们可以观察一下RTL Viewer,如下图:

loop1进程由于使用了for...loop,所以对应RTL Viewer就比较复杂,但是我们可以基本猜出QuartusII综合器的综合流程:

1、有4个“等于”比较器,分别对应Sel输入和常量值;

2、dout(*)输出由4个“二选一”的复选器,选择信号是4个“等于”比较器的输出;

有一个有趣的现象(RTL Viewer):sel = 0时,对应的din[0..3]输出至dout的逻辑延迟最长,sel = 1次之,依次类推...。到次为止,可能很多人会觉得loop1进程所需要的逻辑门比case1的逻辑门多很多,最开始我也这么认为,但是不着急,我们接着看一下Technology Viewer,如下图:

我们可以看到“sel din dout”和“sel din1 dout1”都是各用了8个LUT,逻辑延迟均为2个LUT。由此我们知道:RTL Viewer从某种程度上告诉我们综合器的从RTL代码到基本算法及逻辑单元的算法行为,而Technology Viewer告诉我们综合器的逻辑行为到LC单元的映射。所以,从RTL Viewer判断一个VHDL的描述代码的好坏是有误的。造成上述现象的原因,从我个人的观点,一个4输入LUT,可以描述任何4输入的逻辑表达式,如果用与或门描述各种4输入表达式,相对应的门数和逻辑延迟都不尽相同,但是当最小单元是LUT,则相对应的门数和逻辑延迟都可以认为是一致的,这也许就是ASIC和FPGA的最根本的区别。

最终我的观点是:

1、利用for...loop对设计FPGA IP的参数化配置是有很大帮助的,但是如果在ASIC设计中,设计需求已经确定,for...loop的描述由于其综合过程的复杂性,应该尽量避免;

2、当一个组合逻辑的输入数确定,不论用何种描述方式,其所用的LUT数也就基本确定,这应该是由“聪明”的综合器决定的;

3、RTL Viewer可以帮助你理解你设计的算法,Technology Viewer查看LUT的工作方式。

希望大家一起讨论,及时指证文章中的错误及不易理解的地方,谢谢!

/5

/5

coyoo 2009-5-22 12:19