FPGA的基本单元,其输出直接连至全局时钟网络。真值表如下:

| Inputs | Outputs | ||

|---|---|---|---|

| X | X | F | 0 |

| IO | I1 | S | O |

| I0 | X | 0 | I0 |

| X | I1 | 1 | I1 |

| X | X | R | 0 |

使用VHDL的同学需要导入库unsim:

library unisim;

use unisim.vcomponents.all;

在FPGA中全局时钟资源是有限的,根据自身的应用确定所以全局时钟资源的个数,然后根据时钟管脚的位置约束每个BUFGMUX的位置。约束语句如下:

INST "u4/u1" LOC=BUFGMUX_X1Y11;Xilinx工具支持BUFMUX直接Infer,wind330没有尝试过,但是自己无法控制关键路径,对产生的影响也不可控,所以没有采用。

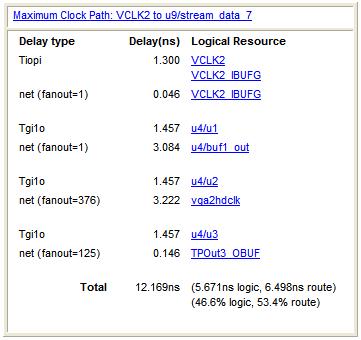

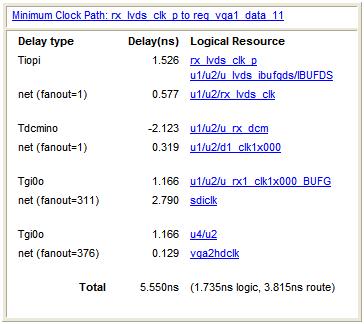

首先说明一下电路功能,电路需要对四个时钟进行片选,分别是vclk1,vclk2,sdiclk,tpout3。对应有3个BUFGMUX,vclk1与vclk2连接一个BUFGMUX,将其输出与sdiclk连接一个BUFGMUX(该BUFGMUX输出为vga2hdclk),vga2hdclk与tpout3连接一个BUFGMUX。下面是两条不同时钟路径的延时说明:

|

| Figure1 vclk2延时详细说明 |

|

| Figure2 sdiclk延时详细说明 |

至此,有人可能会问:该如何缩短这段延时呢?wind330认为:FPGA的架构决定了延时是无法缩短至0.1ns这个级别的。那我们又如何保证同步于vga2hdclk的数据到tpout3时钟域不会造成时序冲突?由于电路功能只是进行数据源选择,也就是说输入数据源和输出数据源的数据率是完全一致的,只是有不同的相位,所以最直接的方法是:添加一级dual clock FIFO,等FIFO半满后,就可以开始读出数据,因为时钟频率一致,也就不会造成FIFO读空或者写满。如果是FPGA高手,可以用FPGA Editor手动布局和布线,保证vga2hdclk的数据到达tpout3同步的寄存器不会造成时序冲突,wind330远没有达到这个水平,如果有人会,请不吝赐教!

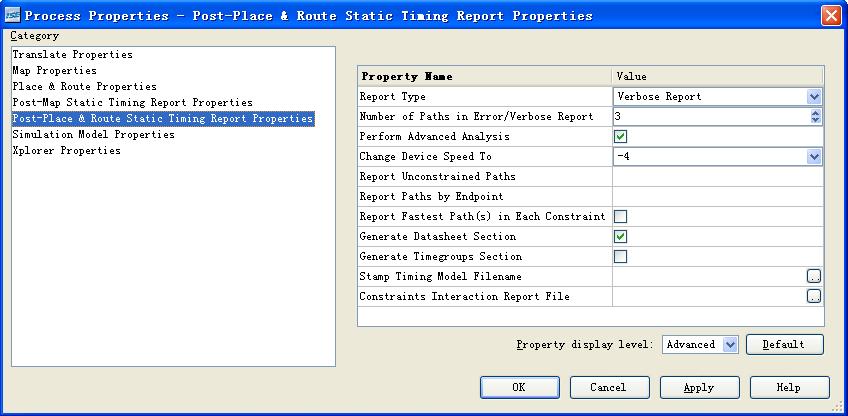

首先,要解决的是时序约束的问题:每个BUFGMUX有两个时钟输入,ISE如何分析相同路径上的不同时钟,下面是Xilinx

网站上关于这种路径的约束设置。

11.1 Known Issue - Timing - Incorrect timing analysis associated with input clocks on BUFGMUX

wind330没有使用上述方法,因为使用的片选时钟频率的上限都是相同的,所以不论满足哪个时钟,我的要求就达到了。但

是,需要在ISE上做好设置,如下图所示

|

| Post-Place & Route Static Timing Report Properties |

在调试过程中曾遇到很奇怪的问题:将上述四个时钟与BUFGMUX连接好后,无论怎么变换输入端S,都没有时钟输出,但是交换每个BUFGMUX的I0,I1输入时钟,上述问题得到解决。呵呵,不知道是否有人与我有相同的遭遇。

/5

/5

用户377235 2016-5-19 20:07