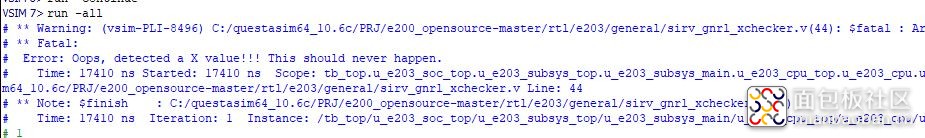

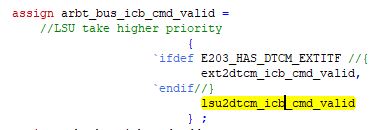

继续trace,发现了一个宏定义的分支:

对于这个宏,E203_HAS_DTCM_EXTITF,看起来应该是DTCM 外部连接ICB。这个e203应该没有连接,所以信号是HiZ,导致X。

试着在e203_defines.v 中 comment掉这个参数,结果报了一堆的error。有些小崩溃。

明天再继续看看怎么回事吧。

继续debug,发现还有个 类似的 E203_HAS_ITCM_EXTITF,也把这个comment掉后,compile 居然过了。

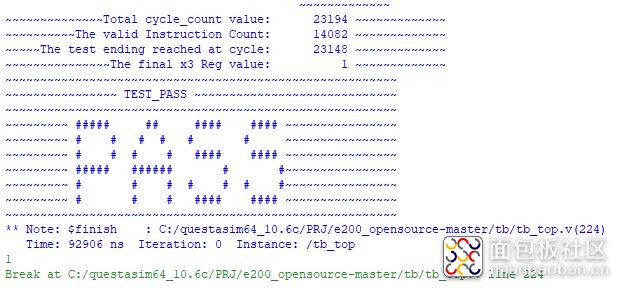

然后跑了一个breakpoint的case,不知道是干什么的,但显示pass。

不知道这些case的说明在什么地方,回头在压缩包里好好找找。

今天又读了里面的一些内容,发现好像这个ALU只支持整形运算,看下面自己能不能加上浮点运算单元。

看来这个RSIC-V能提供的可扩展性确实非常大, 潜力无限,怪不得发展这么迅猛。

看来这本书,我需要好好消化吸收,对未来的工作非常有帮助。说不定干翻ARM的就是它了--------RSIC-V

作者: micoyoung_720270967, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1165720.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

面包板社区管理员 2019-10-28 10:07

Manor 2019-10-28 08:41

申请时间已过。。。

面包板社区管理员 2019-10-25 11:08

Manor 2019-10-25 10:54

curton 2019-10-12 21:42