LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY test IS

port

(

clk : IN STD_LOGIC;

rst : IN STD_LOGIC;

divclk : OUT STD_LOGIC

);

END test;

ARCHITECTURE bdf_type OF test IS

component div

GENERIC (zero:INTEGER);

PORT(clk : IN STD_LOGIC;

rst : IN STD_LOGIC;

clk2 : OUT STD_LOGIC_VECTOR(3 downto 0)

);

end component;

signal clk2 : STD_LOGIC_VECTOR(3 downto 0);

BEGIN

b2v_inst7 : div

GENERIC MAP(zero => 0)

PORT MAP(clk => clk,

rst => rst,

clk2 => clk2);

divclk <= clk2(3);

END;

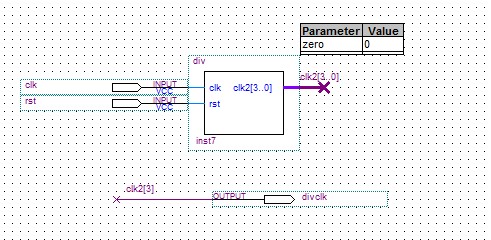

其作用如下原理图

/5

/5

文章评论(0条评论)

登录后参与讨论