用CPLD做的一个高频分频器的干扰问题

<?xml:namespace prefix = o ns = "urn:schemas-microsoft-com:office:office" />

老板布置了一个任务,是给一个100MHz的信号分频,分频分到100kHz。开头他的意思是用74系列做电路,我讥笑他都什么年代了,还用74,所以自己动手用CPLD。其实程序挺简单的,根本没花多少时间就写出来了。

程序如下:

module division(clk,clk10k,reset,outcontrol);

input clk;

input reset;

output clk10k;

output outcontrol;

reg clk10k;

reg outcontrol;

reg[8:0] count="0";

always @(posedge clk)

begin

if(count==499)

begin

count<=0;

clk10k<=~clk10k;

end

else

count<=count+1;

end

always@(posedge clk10k)

begin

outcontrol=reset;

end

endmodule

分频后加了一个D触发器使reset信号与分频后的信号同步。我们也可以通过看综合出来的原理图看到(RTL Schematic)

<?xml:namespace prefix = v ns = "urn:schemas-microsoft-com:vml" />

在做测试时,由于根本没有信号发生器能产生100MHz的信号,于是只好用10MHz,20MHz,30MHz的正弦波代替(由于我们最后也是要对100MHz正弦波分频,其实对于数字电路正弦波和方波都是一样的,TTL电平2.4V以上都是高电平,0.4V以下都算低电平),注意这个正弦波要有直流偏置,不然会有负电压,可能对芯片不好)

结果很不好。

1)当输入信号为30MHz时,分频出来为30kHz,如下图,可以看到有很大的杂波。

把示波器的频率调高,可以看到高电平(或低电平)上叠加了一个周期为34.40ns的波(大概30MHz)。

2)当输入信号为20MHz时,分频出来的方波同样有杂波,很粗。

也可以把频率旋钮调大,可以看到在20kHz的输出信号上叠加了一个50ns(20MHz)的周期性波形。

3)当输入信号为10MHz时,分频出来的波形也同样出现有杂波的情况

有一个100ns(10MHz)的周期性波形

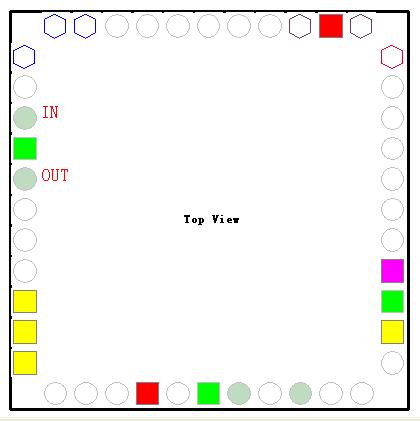

可以看到这些杂波是会随着输入频率的变化而变化的,而又等于输入波的频率,所以可以判定这些杂波是又输入耦合到输出的。经过检查可以知道,最大的原因为输入输出供用了地(也就是输出的信号发生器和输出的示波器的地是连在一起的再连到CPLD的地上。第二个原因是输入输出的线。由于是试验性质的,所以我随手拿了普通排线,定义输入输出管脚的时候也把两个管脚定义在一起。如下图

使得输入的高频信号串扰到输出信号中。总结这些因素如下,重要性如排序先后:

1. 输入输出用地

解决办法:输入输出不接一个地上,分别接CPLD的不同地管脚。

2. 普通排线,平行输入

解决办法:把排线撕开,使之远离。最好的办法是用带屏蔽的同轴线。并使线缆尽量短。

3. CPLD输入输出管脚定义太近

定义管脚的时候要尽量原理,高频的输入信号管脚尽量远离输出管脚及其他敏感信号管脚。

这个在设计PCB板的时候也是重点考虑的因素。

把这些措施都做了之后,可以看到输出波形大为改善。

10MHz输入频率的时候

30MHz输入频率的时候

从以上可以看到输出的杂波的幅值大小都明显减少。要跟彻底地解决高频串扰的问题,还可以在输出加一个高频滤波器(因为我们要的是高频分频1000份之一的低频),或者加磁珠等等。

用户377235 2012-5-18 17:33

用户1168877 2011-8-20 17:11

用户362754 2011-8-3 20:58

用户322840 2011-4-22 21:37

用户563753 2011-2-14 10:40

用户234619 2010-4-26 12:46

用户195584 2010-4-26 10:30

tengjingshu_112148725 2010-4-25 18:06

用户234619 2010-4-24 19:50

用户234619 2010-4-24 19:41